Sự trỗi dậy và sụp đổ của 4 máy tính hàng không vũ trụ Pi của IBM: một lịch sử minh họa

The rise and fall of IBM's 4 Pi aerospace computers: an illustrated history

Hệ thống máy tính System/4 Pi của IBM, ra mắt năm 1967, là một dòng máy tính mạnh mẽ, có độ bền cao, được thiết kế cho các ứng dụng hàng không và quân sự khắt khe, bao gồm cả việc cung cấp năng lượng cho các hệ thống bay quan trọng của tàu con thoi Space Shuttle. Những cỗ máy này mang hiệu năng và độ tin cậy ở cấp độ mainframe đến các môi trường embedded, một kỳ tích kỹ thuật đáng kể vào thời điểm đó. Các nhà phát triển có thể học hỏi từ triết lý thiết kế của dòng 4 Pi về khả năng tính toán chuyên biệt, mạnh mẽ và tầm quan trọng của tài liệu đầy đủ để hiểu biết về lịch sử và kỹ thuật.

Sáng ngày 12 tháng 4 năm 1981, 20 năm kể từ ngày Yuri Gagarin trở thành người đầu tiên bay vào vũ trụ, Tàu con thoi lao vút lên bầu trời Florida. Chỉ huy Young và phi công Crippen đang ở vị trí điều khiển...

Sáng ngày 12 tháng 4 năm 1981, 20 năm sau ngày Yury Gagarin trở thành người đầu tiên bay vào vũ trụ, Tàu con thoi lao vút lên bầu trời Florida. Chỉ huy Young và Phi công Crippen điều khiển khi Tàu con thoi cất cánh trong chuyến bay đầu tiên. Nhưng quá trình phóng, giống như phần lớn chuyến bay, thực sự được điều khiển bởi bốn máy tính trong khoang điện tử hàng không. một boong bên dưới thủy thủ đoàn. Chiếc máy tính thứ năm sẵn sàng tiếp quản trong trường hợp máy tính gặp sự cố nghiêm trọng. Những máy tính này, Model AP-101B, là một phần của dòng System/4 Pi của IBM.

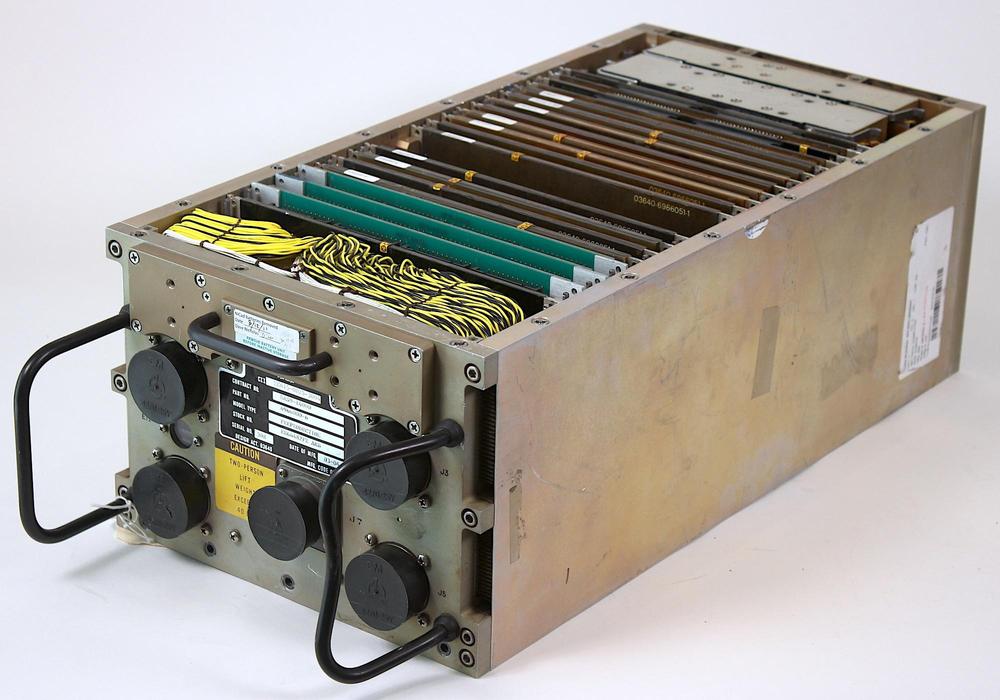

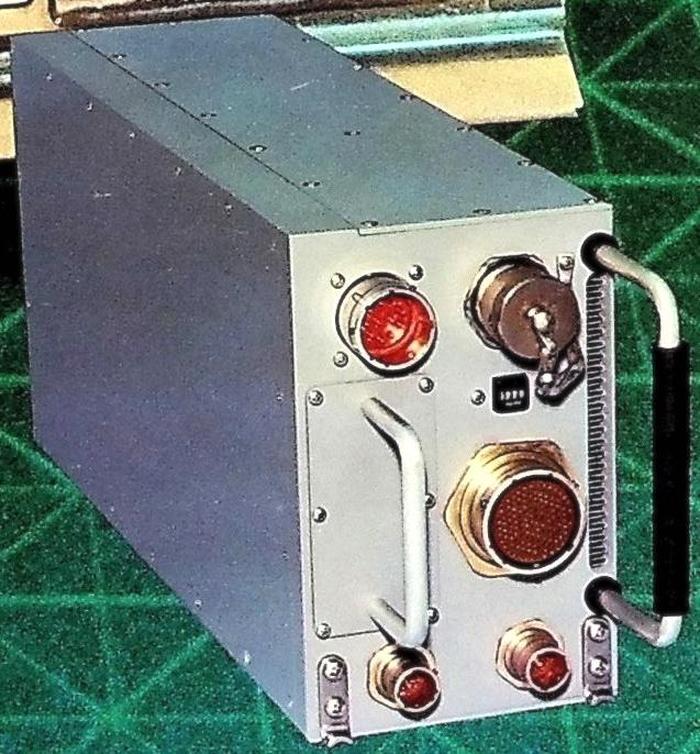

Máy tính tàu con thoi AP-101B. Thiết bị này đã bay trên nhiều chuyến bay, bao gồm STS-38 (1990) và STS-40 (1991). Hình ảnh được cung cấp bởi Đấu giá RR.

Được giới thiệu vào khoảng năm 1967, dòng System/4 Pi là dòng máy tính nhỏ gọn, mạnh mẽ được thiết kế cho hệ thống điện tử hàng không các vai trò. Quân đội đã sử dụng những máy tính này trong mọi thứ, từ máy bay chiến đấu F-4 và máy bay ném bom B-52 cho đến hệ thống sonar tàu ngầm và tên lửa chống hạm Harpoon. Các máy tính khác trong dòng System/4 Pi đóng vai trò hòa bình hơn trong việc phát triển GPS và chuyến bay điện tử điều khiển. Trong không gian, máy tính System/4 Pi điều khiển Skylab, trạm vũ trụ đầu tiên của Mỹ, cũng như Spacelab, trạm vũ trụ có thể tái sử dụng. phòng thí nghiệm được điều khiển bởi Tàu con thoi.

Mặc dù máy tính System/4 Pi có vai trò quan trọng nhưng rất khó lấy được thông tin—Wikipedia hoàn toàn bỏ qua các mô hình CC, SP và ML. 1 Tuy nhiên, tôi đã nhận được một chồng tài liệu và bài báo tiếp thị 4 Pi, vì vậy Bây giờ tôi có thể lấp đầy nhiều khoảng trống trong lịch sử của System/4 Pi.

Thế hệ đầu tiên

Dòng máy tính lớn IBM System/360 được giới thiệu vào năm 1964. System/360 đã cách mạng hóa ngành công nghiệp máy tính với khái niệm về một dòng máy tính cho tất cả các ứng dụng: kinh doanh và khoa học. Cái tên tượng trưng cho System/360 bao phủ đầy đủ 360 độ của ứng dụng. Tên 4 Pi đã mở rộng ý tưởng này cho các ứng dụng trong thế giới 3 chiều: 4π là số steradian tạo nên một hình cầu đầy đủ. Như IBM đã nói, "System/4 Pi cũng đáp ứng đầy đủ các nhu cầu về máy tính quân sự - để sử dụng trên không, trong không gian hoặc trên tàu."

Ban đầu, dòng System/4 Pi có ba mẫu: "Mẫu TC (máy tính chiến thuật) dành cho vệ tinh, tên lửa chiến thuật, máy bay trực thăng và các ứng dụng khác yêu cầu máy tính rất nhỏ, nhẹ; Model CP (bộ xử lý tùy chỉnh) dành cho các ứng dụng điện toán thời gian thực; và Model EP (hiệu năng mở rộng) dành cho các ứng dụng yêu cầu tính toán theo thời gian thực với lượng dữ liệu rất lớn." 2

Máy tính chiến thuật TC

Máy tính chiến thuật TC là một máy tính kỹ thuật số đa năng, được thiết kế để có hiệu suất tầm trung và chi phí thấp (chi tiết ). TC có word 16 hoặc 32 bit nhưng sử dụng bus 8 bit để giảm chi phí. Nó hỗ trợ bộ nhớ lõi từ 8 KB đến 64 KB. Nó có một tập lệnh đơn giản với tổng cộng 54 lệnh, bao gồm cả nhân và chia. Như thường lệ vào thời điểm đó, nó không có ngăn xếp cho các lệnh gọi chương trình con mà thay vào đó có lệnh chi nhánh và cửa hàng. Mô hình ban đầu chạy 48.500 lệnh mỗi giây. Trong khi điều này chậm kinh khủng theo thời hiện đại tiêu chuẩn, đó là hiệu suất ở cấp độ máy tính lớn vào thời điểm đó, có thể so sánh với máy tính lớn IBM 360/40 tầm trung.

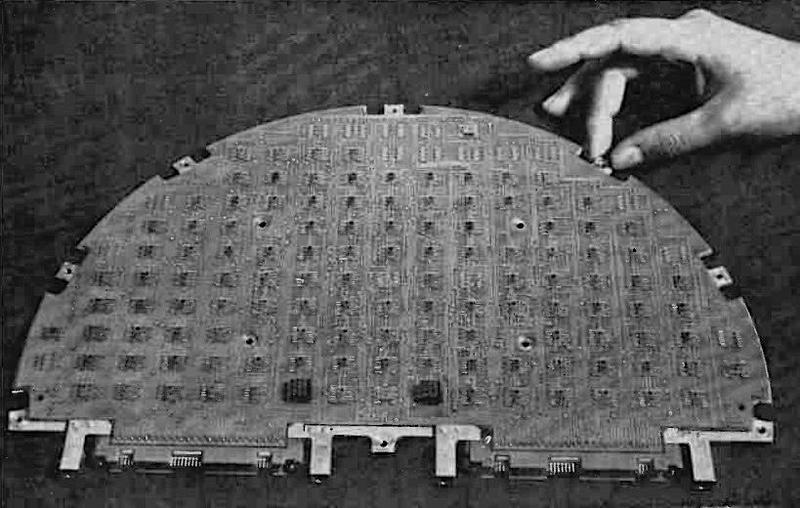

Tập hợp con số học và điều khiển của máy tính TC, được cấu hình cho tên lửa chiến thuật. Từ Electronics, ngày 6 tháng 3 năm 1967. Xem thêm Điện tử, ngày 10 tháng 10 năm 2017. 31, 1966.

TC ban đầu được đóng gói trong một hộp cỡ cặp tài liệu (9,75" × 17,12" × 4,0") (bên dưới) nặng 17,3 pound nhưng có thể được đóng gói lại cho các ứng dụng khác nhau. Đối với tên lửa chiến thuật, máy tính được triển khai trên các bảng mạch hình bán nguyệt như hình trên. Máy tính được xây dựng từ TTL (Transistor-Transistor Logic) 3 mạch tích hợp gói phẳng được gắn trên bảng mạch bốn lớp. Hai bảng mạch tạo thành một lớp bánh sandwich bao quanh một cấu trúc kim loại nhằm hỗ trợ và làm mát; tổ hợp ba lớp này là gọi là "trang". Một trang có thể chứa khoảng 300 mạch tích hợp nên máy tính rất dày đặc.

Máy tính TC-1 đóng vai trò quan trọng trong Skylab, trạm vũ trụ đầu tiên của Mỹ được phóng vào năm 1973.4 Hướng của Skylab cần phải được kiểm soát chính xác để nhắm vào nhiều kính thiên văn của nó. Để tránh tiêu thụ nhiên liệu đẩy, Skylab được quay bằng cách thay đổi tốc độ của ba con quay hồi chuyển lớn, Mỗi cái 155 bảng. Hai máy tính TC-1 điều khiển các con quay hồi chuyển này, với một máy tính đang hoạt động và một máy tính dự phòng. Mỗi máy tính 16 bit có 16K từ lưu trữ có thể được tải lại từ băng từ hoặc radio, và thực hiện 60.000 thao tác mỗi thứ hai. Mỗi máy tính Skylab chiếm 2,2 feet khối (lớn hơn nhiều so với TC cỡ cặp sách) và nặng 97,5 pound. Máy tính Skylab nổi bật là hệ thống điều khiển kỹ thuật số hoàn toàn đầu tiên trên tàu vũ trụ có người lái.

Mẫu TC-2 (bên dưới) nhanh hơn nhiều (125.000 thao tác mỗi giây) và nặng 80 pound. Nó được sử dụng để dẫn đường/cung cấp vũ khí trên máy bay chiến đấu tấn công A-7D/E. Vào năm 1976, nó được được nâng cấp lên TC-2A, vẫn nhanh hơn (454.000 thao tác mỗi giây), hỗ trợ nhiều bộ nhớ hơn và thêm 12 lệnh nữa.

Một máy tính TC-2, cụ thể là Máy tính Điều khiển Bộ Kiểm tra CP-993/ASM. Nó trông giống như máy tính CP-952/ASN-91(V) của máy bay A-7. Hình ảnh được cung cấp bởi Alex1970-14; máy tính này hiện có trên eBay nếu bạn muốn.

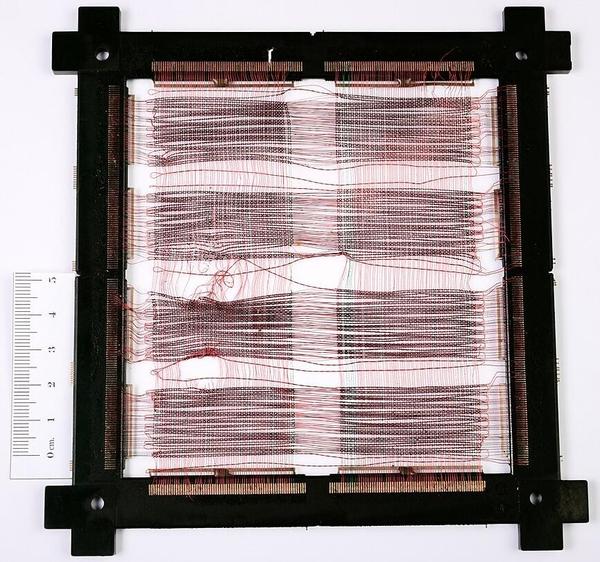

Giống như hầu hết các máy tính cùng thời, TC sử dụng bộ nhớ lõi từ; mỗi bit được lưu trữ trong một lõi hình xuyến nhỏ bằng lithium niken ferit, nối thành lưới.5 Các mặt phẳng lõi trong TC và các máy tính 4 Pi thế hệ đầu tiên khác có cạnh khoảng 6 inch. Với 16.384 lõi trong một mặt phẳng, mỗi mặt phẳng chứa 16 Kbit. Do đó, bộ nhớ 8 kilobyte trong TC yêu cầu một chồng bốn mặt phẳng lõi. Một lợi thế đáng kể của bộ nhớ lõi là vì nó có từ tính nên dữ liệu được bảo toàn ngay cả khi bộ nhớ không được cấp nguồn. Nó cũng có khả năng chống bức xạ cao.

Mặt phẳng bộ nhớ lõi (hơi bị hư hỏng) này là phiên bản thương mại của các mặt phẳng trong máy tính System/4 Pi thế hệ đầu tiên. Ảnh của José Luis Briz Velasco, CC BY-SA 4.0, đã cắt.

Bộ xử lý tùy chỉnh CP

Một bước tiến so với dòng TC là Bộ xử lý tùy chỉnh CP (gọi tắt là Hiệu suất chi phí).6 Nó sử dụng CPU 16 bit, nhưng có bus 36 bit rộng tới bộ nhớ để có hiệu suất cao hơn (bao gồm hai bit chẵn lẻ và hai bảo vệ lưu trữ 7 bit). Không giống như dòng TC, dòng CP được mã hóa nội bộ (tùy chọn) nên có thể dễ dàng tùy chỉnh bộ hướng dẫn.8 Hệ thống CP có các định dạng hướng dẫn hoàn toàn khác với hệ thống TC. 10 Mô hình cơ sở có 36 lệnh và thực hiện 91.000 lệnh mỗi giây. CP hỗ trợ nhiều chế độ đánh địa chỉ, nâng cao hơn so với cách đánh địa chỉ đơn giản của hệ thống TC. Trong khi TC chạy ở tần số 330 kHz thì CP chạy ở tần số 2,4 megahertz. Hiệu suất của CP không được cải thiện đồng hồ nhanh hơn sẽ gợi ý nhiều như vậy vì cả hai hệ thống đều sử dụng bộ nhớ lõi chậm.

Máy tính IBM CP. từ tài liệu quảng cáo "Hệ thống IBM/4 Pi Model CP", 1967.

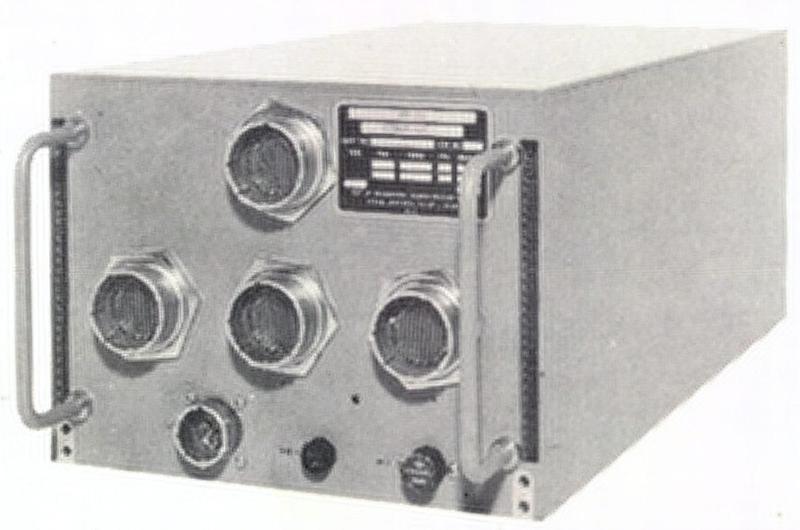

Một trong những điểm mạnh của System/4 Pi là đầu vào/đầu ra, cho phép nó giao tiếp với các thiết bị bên ngoài trong thời gian thực. CP-1 có khả năng I/O mở rộng: ba đầu vào song song tốc độ cao, một đầu ra song song tốc độ cao, một đầu ra nối tiếp, 24 đường đầu vào riêng biệt, 144 dòng đầu ra riêng biệt và 24 dòng ngắt. Để hỗ trợ tất cả các tín hiệu I/O này, CP-1 được đóng gói trong hai hộp: một hộp dành cho chính máy tính và một hộp dành cho giao diện I/O. các Hộp CPU được hiển thị bên dưới; hộp ghép nối I/O cũng tương tự, nhưng mặt trước có hơn chục đầu nối cho các đường I/O. CP-1 được sử dụng trong hệ thống phân tích mối đe dọa/dẫn đường trên máy bay tác chiến điện tử EA-6B Prowler.9

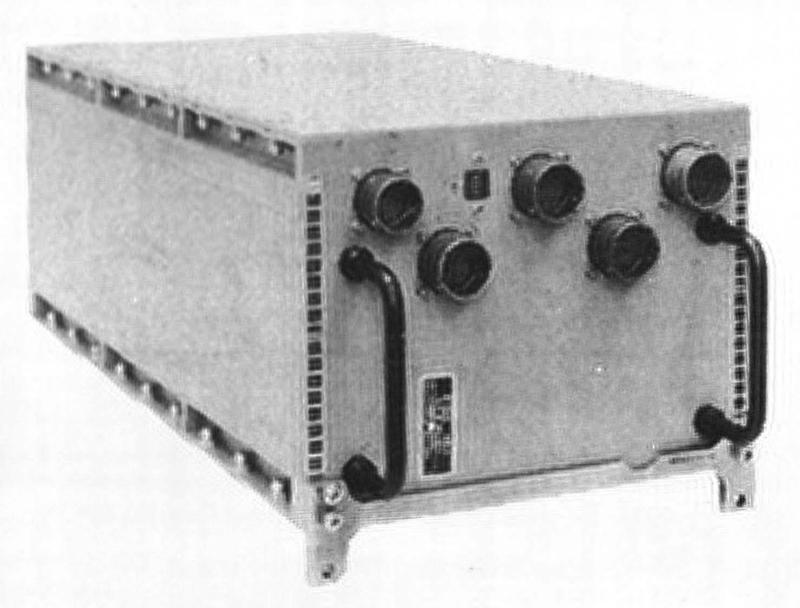

Máy tính CP-1, được chỉ định là CP-926/AYA-6. Từ tài liệu quảng cáo "Hệ thống IBM/4 Pi và Hệ thống nâng cao/Máy tính 4 Pi", tháng 8 năm 1973.

CP-2 là máy tính dẫn đường/cung cấp vũ khí trên máy bay chiến đấu F-111, tích hợp radar và vũ khí. Nó nhanh hơn CP-1, có lẽ vì nó không được lập trình vi mô, thực hiện 150.000 lệnh mỗi giây. Nó cũng nhỏ hơn, chiếm một hộp nặng 47 pound, mặc dù nó có ít hỗ trợ I/O hơn. Thật không may, chiếc máy tính F-111 này được cho là là một thảm họa về mặt hoạt động vì máy tính có vấn đề về độ tin cậy và hiệu suất hạn chế. CP-2 sau đó được thay thế bằng CP-2EX cải tiến.

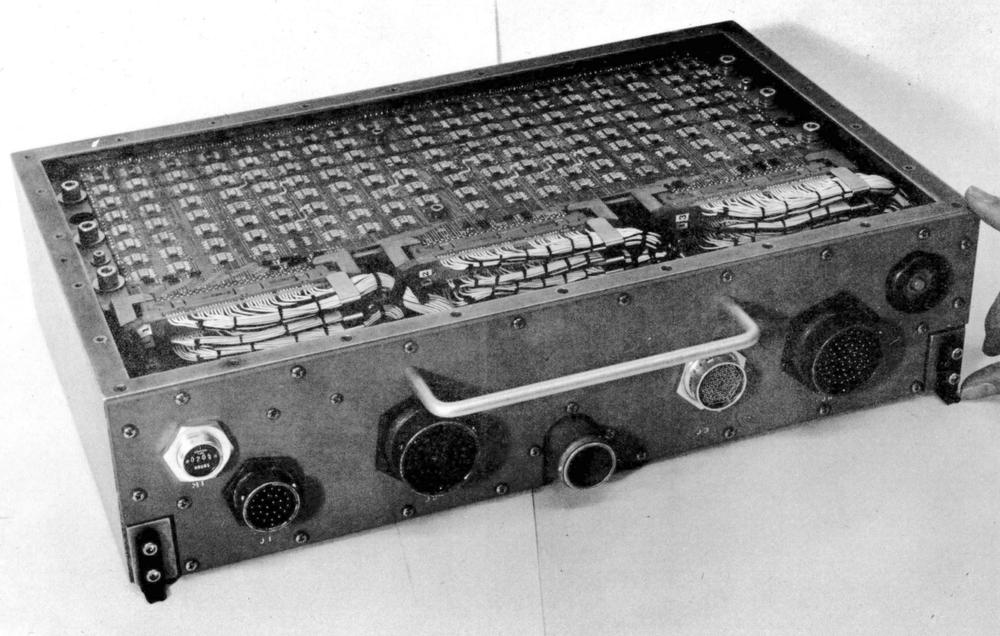

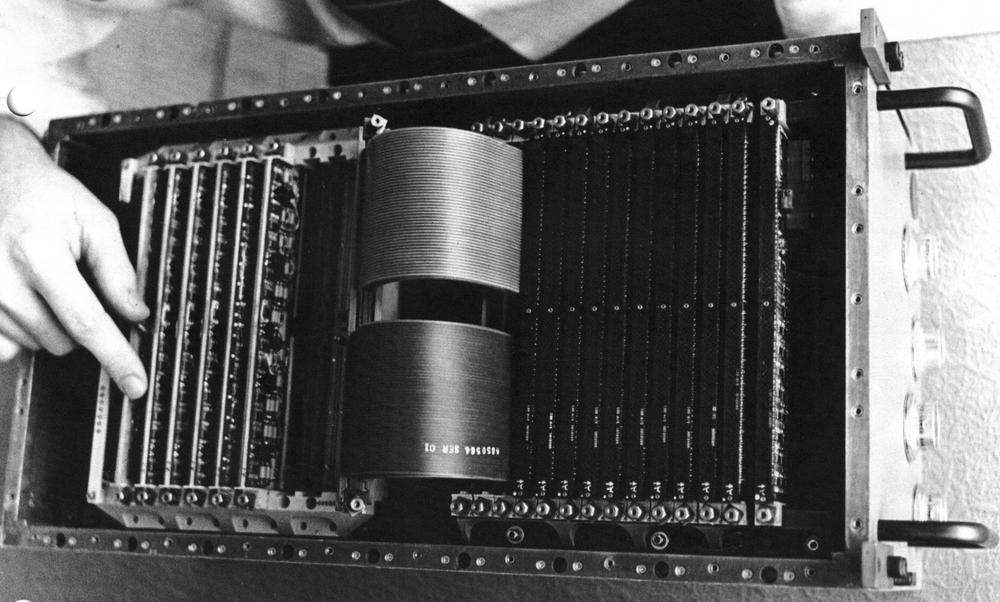

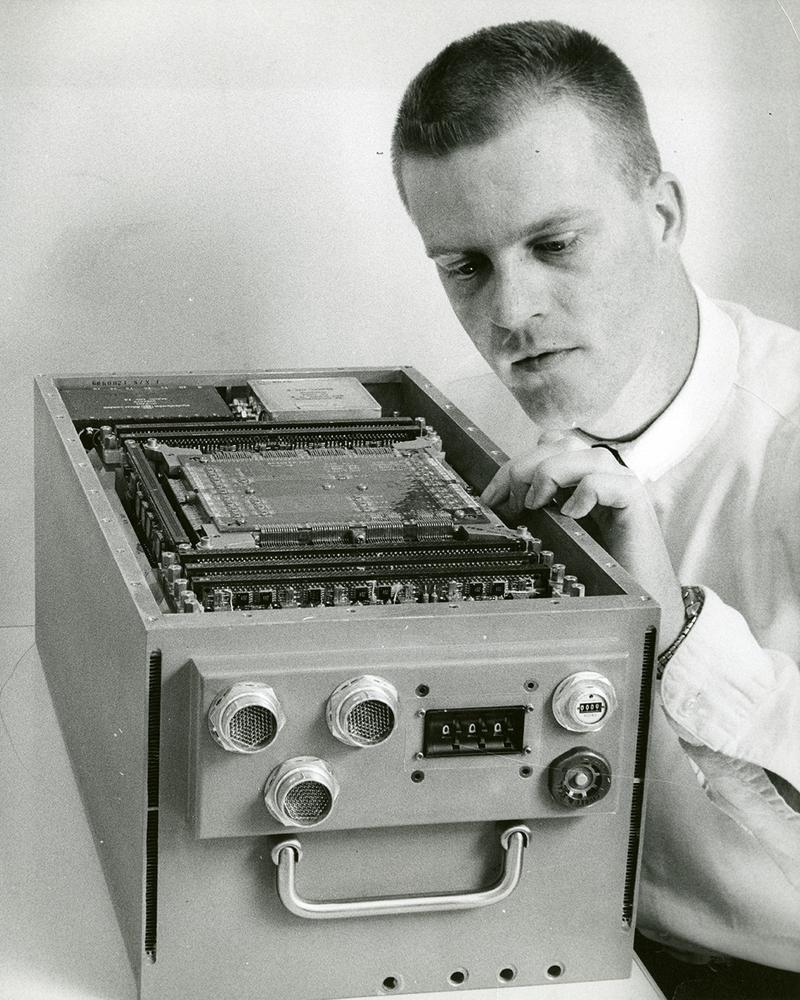

Máy tính CP-2, được chỉ định là AN/AYK-6. Mặt số ba chữ số ở mặt trước đã được che và buộc chặt bằng dây an toàn trước khi sử dụng nên chắc chắn nó rất quan trọng. Ngăn xếp bộ nhớ lõi nằm ở giữa máy tính, có dung lượng lưu trữ từ 8K đến 16K từ. Các trang mạch ở phía trước. Ảnh từ Thread của IBM, cũng hiển thị một máy tính TC-2 đã được tháo rời.

Máy tính CP-3 (bên dưới) được sử dụng để điều hướng và cung cấp vũ khí trên máy bay A-6E Intruder (1970) và các máy bay khác, thay thế máy tính Litton trước đó bằng bộ nhớ trống không đáng tin cậy. Máy tính này có thể được tích hợp với bom "thông minh" dẫn đường bằng laser. Nó tương tự như CP-2 và có cùng hiệu suất nhưng có các chức năng I/O khác nhau.

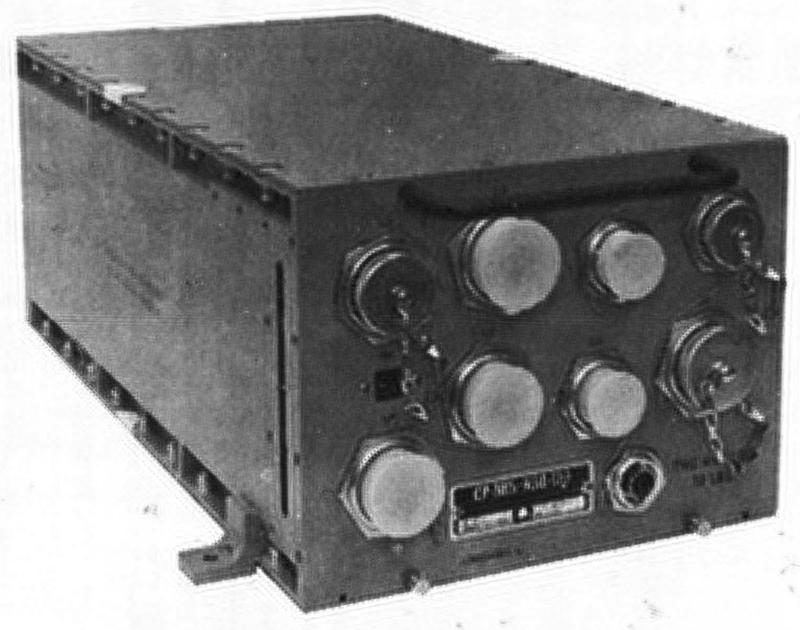

Máy tính CP-3, được chỉ định là CP-985/ASQ-133. Từ tài liệu quảng cáo "Hệ thống IBM/4 Pi và Hệ thống nâng cao/Máy tính 4 Pi", tháng 8 năm 1973.

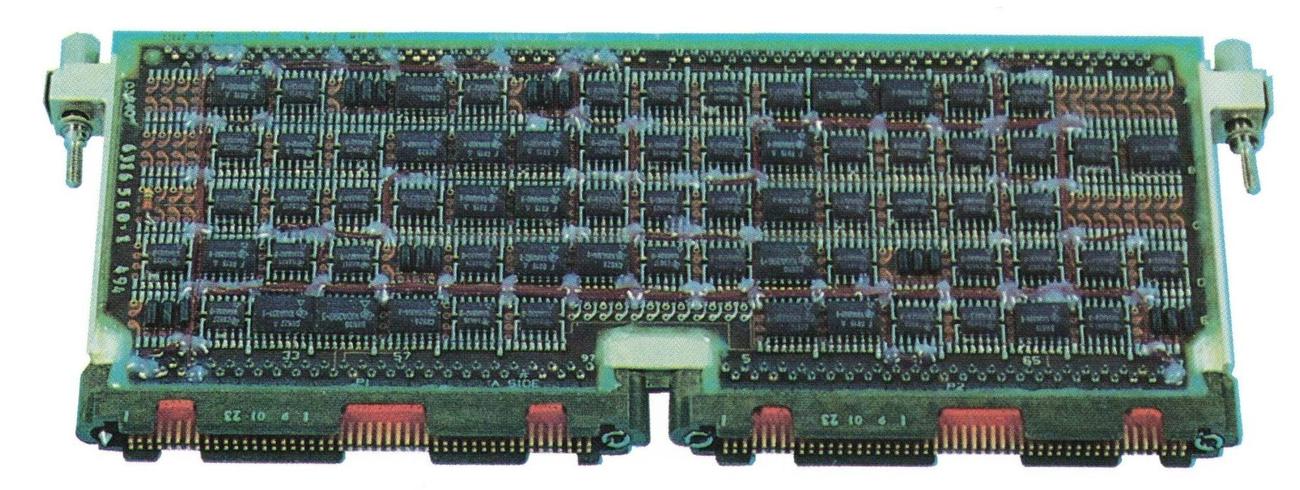

Giống như TC, CP được chế tạo từ các chip TTL đóng gói phẳng gắn trên bảng mạch gọi là "trang". Tuy nhiên, CP đã sử dụng các trang nhỏ hơn với sáu lớp thay vì bốn; mỗi trang hai mặt có thể chứa tới 156 mạch tích hợp. Mỗi trang có hai đầu nối 98 chân, sử dụng lại kiểu đầu nối mà IBM đã sử dụng trong Apollo cho Vụ phóng tên lửa Saturn V Máy tính kỹ thuật số xe (LVDC). IBM đã tiêu chuẩn hóa loại trang này trong nhiều thập kỷ; trang bên dưới đã được sử dụng trong máy tính AWACS (1991) và gần giống với các trang trong máy tính CP năm 1967.

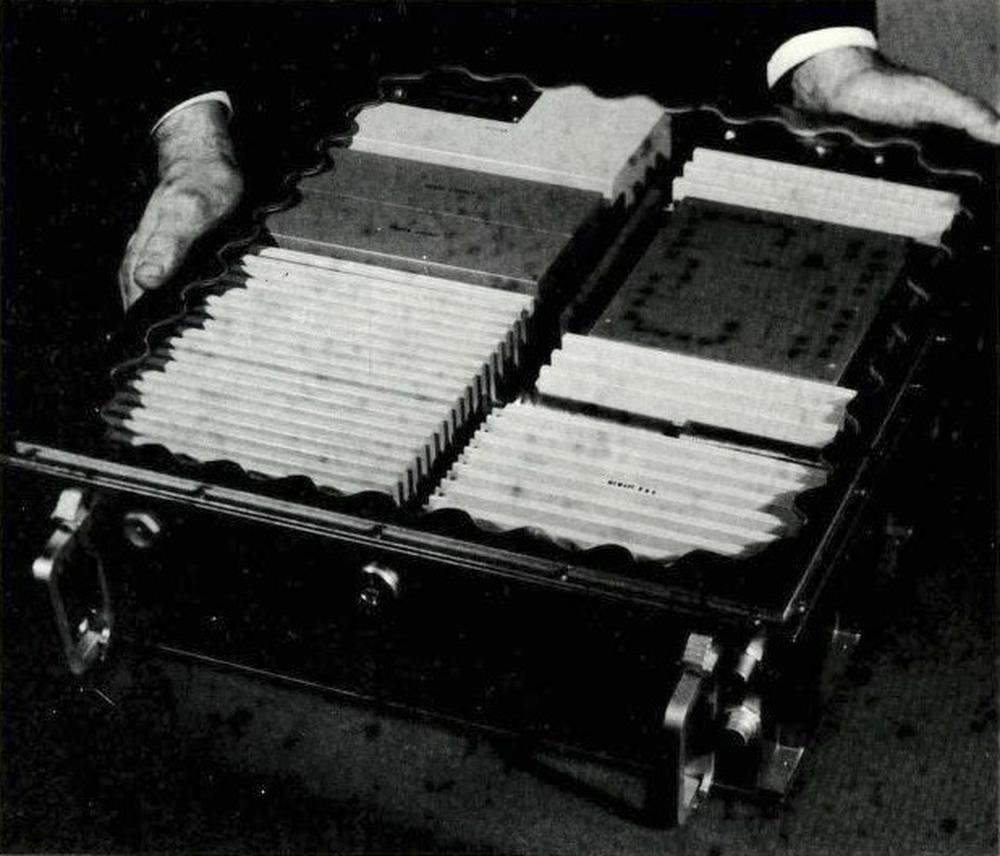

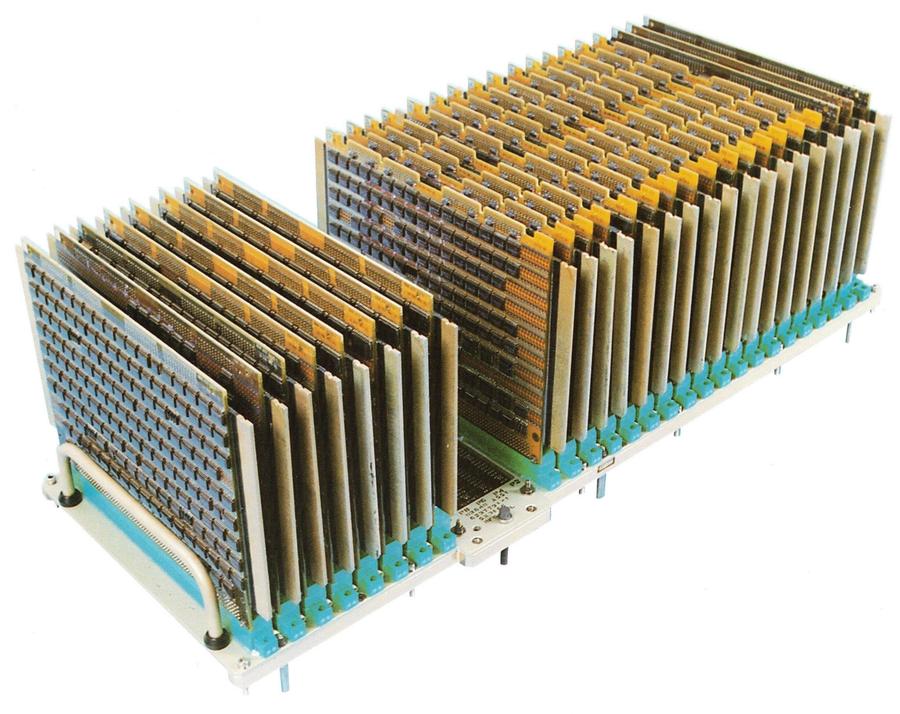

Một tập hợp trang Hệ thống IBM/4 Pi tiêu chuẩn. Từ tài liệu "Hệ thống con xử lý dữ liệu AWACS", 1991.

Máy tính EP (Hiệu suất mở rộng)

EP là máy tính mạnh nhất trong số các máy tính System/4 Pi ban đầu. Đó là một máy tính 32-bit tương thích với các máy tính lớn IBM System/360, cụ thể là 360 Model 44.11 Đối với đầu vào/đầu ra, EP sử dụng kiến trúc kênh I/O giống như các máy tính lớn System/360. Để hỗ trợ tập lệnh 360 phức tạp, EP đã được mã hóa vi mô. Nó thực hiện 190.000 lệnh mỗi giây và nặng 75 pound. Hỗ trợ dấu phẩy động có sẵn dưới dạng tùy chọn.

Phiên bản đa bộ xử lý của EP, EP/MP, hỗ trợ tối đa ba CPU chia sẻ bộ nhớ. Nó được giao cho Phòng thí nghiệm quỹ đạo có người lái (MOL) của Không quân, nhưng MOL dự án đã bị hủy ( chi tiết). Hệ thống đa bộ xử lý cũng được sử dụng cho dự án nghiên cứu chống tàu ngầm VS ANEW, một phần của chương trình VSX dẫn đến sự ra đời của Lockheed S-3 Viking, một loại máy bay sử dụng máy tính System/4 Pi SP-0A thay vì EP.

Thế hệ tiếp theo: Advanced System/4 Pi

Đầu năm 1970, IBM đã tạo ra dòng Advanced System/4 Pi.12 Các hệ thống 32 bit này nhanh hơn, nhỏ hơn và tiên tiến hơn đáng kể so với các máy tính System/4 Pi trước đó. Những máy tính này tận dụng các mạch tích hợp cải tiến, được gọi là Tích hợp quy mô trung bình (MSI). Các mạch tích hợp này chứa từ 10 đến 100 cổng trên mỗi chip, so với các mạch trước đó. Chip tích hợp quy mô nhỏ (SSI) có từ 1 đến 10 cổng trên mỗi chip, cho phép chip thực hiện các công việc phức tạp hơn chức năng, chẳng hạn như một thanh ghi thay đổi, bộ đếm hoặc bộ cộng.) Hơn nữa, những máy tính này sử dụng bộ nhớ lõi nhanh hơn, giảm thời gian chu kỳ bộ nhớ từ 2,5 µs xuống còn 1 µs.

Loạt bài này ban đầu bao gồm ba dòng: Bộ xử lý nâng cao (AP), Bộ xử lý hệ thống con (SP) và Lệnh và Kiểm soát (CC). Dòng AP là dòng lớn nhất và nổi tiếng nhất, cung cấp năng lượng cho Tàu con thoi cũng như nhiều máy bay. Vài năm sau, IBM giới thiệu dòng ML. Mặc dù các dòng SP, CC và ML là mơ hồ, họ có một số tính năng thú vị.

Bộ xử lý nâng cao (AP)

Phần lớn, các máy tính AP sử dụng tập lệnh và kiến trúc bắt nguồn từ System/360, được gọi là MMP (Bộ xử lý đường giữa đa năng).13 Không giống như các máy tính EP, Máy tính AP không tương thích với System/360: định dạng lệnh, thanh ghi, chế độ địa chỉ, và các mã điều kiện là khác nhau. Một số máy tính AP sử dụng tập lệnh 16-bit theo Tiêu chuẩn của Không quân, được gọi là MIL-STD-1750A.

Dòng Bộ xử lý nâng cao bắt đầu với AP-1, bộ xử lý 32 bit thực hiện 450.000 lệnh mỗi giây và nặng 36 pound. Nó có thể được lập trình bằng trình biên dịch mã hoặc ngôn ngữ JOVIAL của quân đội. Nó hỗ trợ 16K Halfwords đến 64K Halfwords dung lượng lưu trữ bên trong và có thể thêm nhiều hơn nữa vào hộp bên ngoài. Nó có bốn kênh I/O tốc độ cao, xử lý tối đa 15 thiết bị trên mỗi kênh. Điểm nổi có sẵn dưới dạng tùy chọn. AP-1 được mô tả chi tiết tại đây.

Máy tính AP-1, được chỉ định CP-1075/AYK. Từ tài liệu quảng cáo "Hệ thống IBM/4 Pi và Hệ thống nâng cao/Máy tính 4 Pi", tháng 8 năm 1973.

Máy tính AP-1 được sử dụng trong máy bay chiến đấu F-15 để điều hướng/cung cấp vũ khí và quản lý dữ liệu. Nó cũng được Nhật Bản sử dụng trong máy bay chiến đấu F-4. Một máy tính được nâng cấp, AP-1R, có bộ nhớ lõi 256K và thực hiện hơn 1 triệu lệnh mỗi giây; nó được sử dụng trên máy bay F-15E vào năm 1983. AP-1A đã được sử dụng để phát triển AWACS Seek Bus hệ thống liên lạc chiến thuật và Hệ thống phân phối thông tin chiến thuật chung (JTIDS).

Máy tính AP-2 gần giống với AP-1 về hình dáng và chức năng, với một số thay đổi về khả năng I/O của nó. Nó được sử dụng trong Hệ thống thử nghiệm tích hợp trung tâm (CITS) trên máy bay ném bom B-1 để cung cấp thử nghiệm và khắc phục sự cố theo thời gian thực (chi tiết).

Máy tính AP-101 đã mở rộng tập lệnh của AP-1 từ 83 lên 151, cũng như có bộ nhớ lõi nhanh hơn một chút. Chín máy tính AP-101 đầu tiên được sử dụng trong chương trình nghiên cứu kỹ thuật số fly-by-wire của NASA sử dụng máy bay chiến đấu F-8 (link ). AP-101 cũng được sử dụng để phát triển GPS.

Máy tính AP-101. Từ tài liệu quảng cáo "Hệ thống IBM/4 Pi và Hệ thống nâng cao/Máy tính 4 Pi", tháng 8 năm 1973.

Khoảng năm 1975, máy tính AP-101B được phát triển cho Tàu con thoi.14 Bước đầu tiên là cải tiến tập lệnh để hỗ trợ "ngôn ngữ bậc cao" tốt hơn, tạo ra AP-101A. Tiếp theo, bộ nhớ lõi mật độ gấp đôi được sử dụng, tạo ra AP-101B mà Tàu con thoi đã sử dụng trong nhiều năm. Máy tính AP-101B được hợp tác với IOP (Bộ xử lý I/O), về cơ bản là máy tính thứ hai xử lý I/O, cung cấp 24 bus dữ liệu cho phần còn lại của Tàu con thoi. Để đảm bảo độ tin cậy, Tàu con thoi có bốn Máy tính AP-101B chạy song song và được biểu quyết trên mỗi đầu ra, do đó máy tính bị lỗi có thể bị loại trừ. Hơn nữa, chiếc máy tính thứ năm đã sẵn sàng để dự phòng, sử dụng phần mềm được lập trình độc lập trong trường hợp có sự cố. lỗi phần mềm khiến cả bốn máy tính chính đều bị lỗi.15

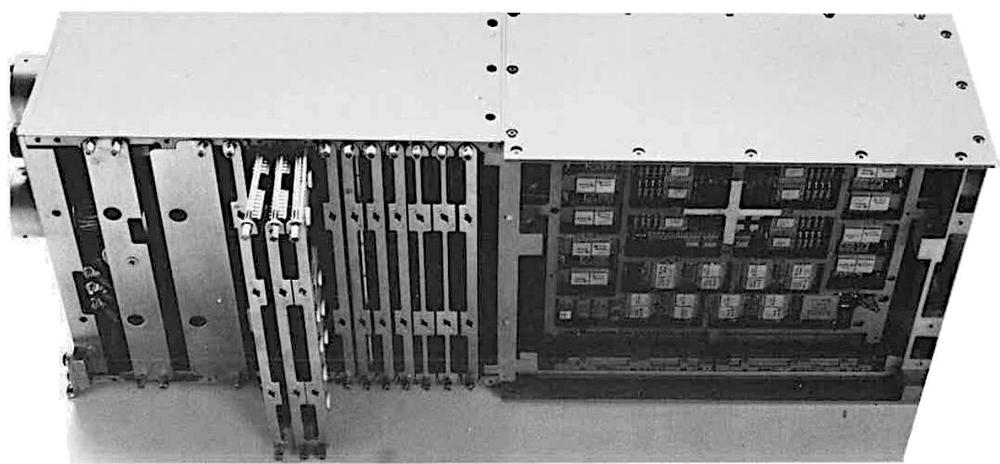

Bộ xử lý I/O của tàu con thoi (IOP, trái) và máy tính AP-101B (phải). Hình ảnh được cung cấp bởi Đấu giá RR.

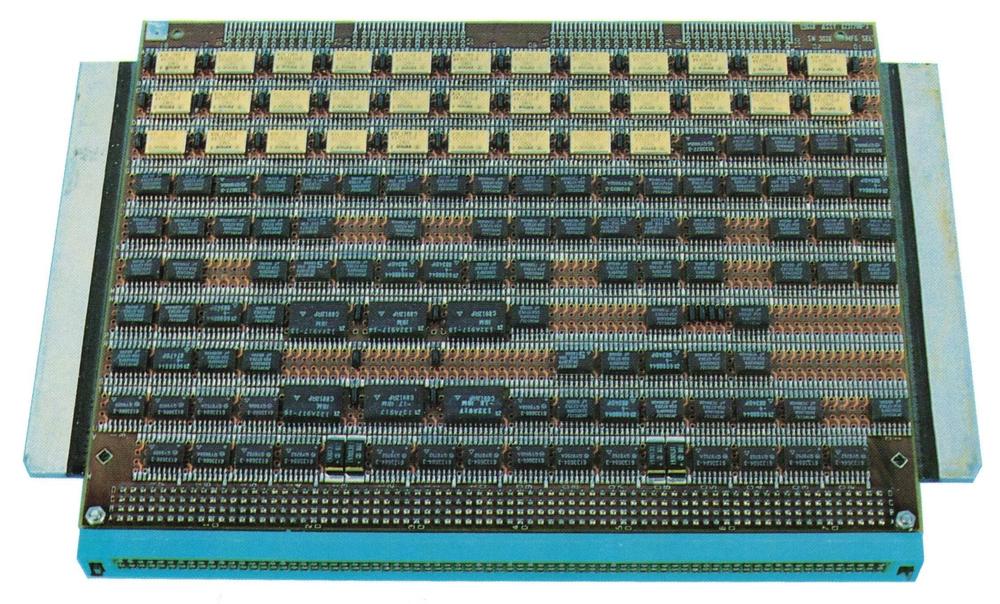

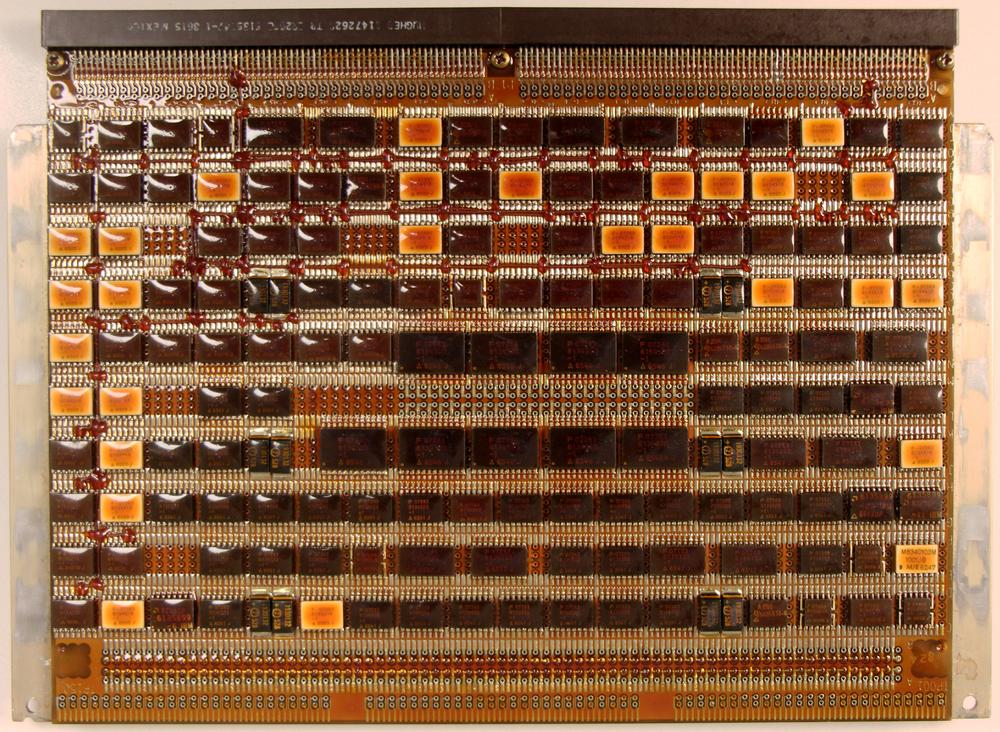

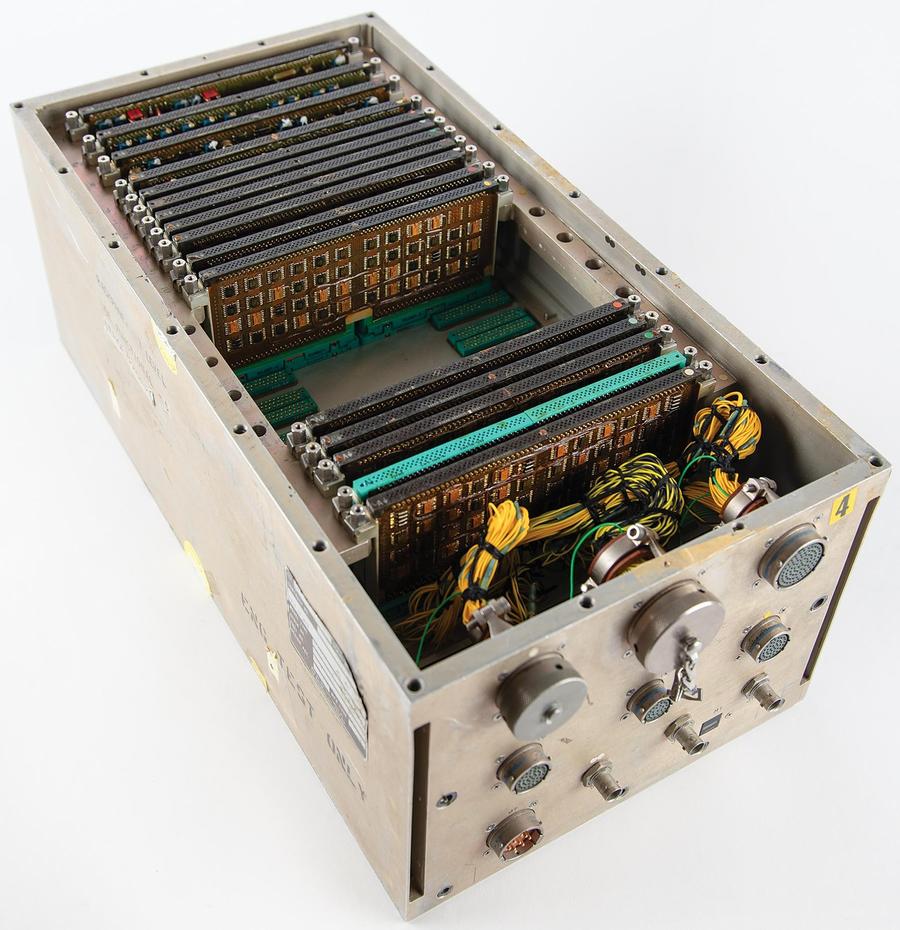

Máy tính Space Shuttle có bộ nhớ 104K từ 32 bit. AP-101B chứa mười trang bộ nhớ (tức là bảng mạch), mỗi trang chứa 16K×18 bit, trong khi IOP chứa sáu trang, mỗi trang chứa 8K×18 bit. 16 Mặc dù bộ nhớ được phân chia vật lý giữa hai hộp nhưng nó hoạt động như một bộ nhớ dùng chung thống nhất.

Mô-đun EP/MCM (Hiệu suất mở rộng/Bộ nhớ lõi mô-đun) của Tàu con thoi lưu trữ 8K x 18 bit (chi tiết). Đây là trang có dung lượng thấp hơn, từ IOP hoặc từ phiên bản đầu tiên của AP-101. Trang này mở ra với các mặt phẳng cốt lõi bên trong. Ảnh từ klabs.

Máy tính AP-101C (1977) có nhiều cải tiến: bộ nhớ lõi mô-đun mật độ gấp bốn lần, công nghệ logic được nâng cấp, và đóng gói lại để giảm chi phí.17 AP-101C có bộ nhớ lưu trữ 32K từ và chạy với hơn 500.000 thao tác mỗi giây.18 AP-101C được sử dụng trong Hệ thống dẫn đường và ném bom kỹ thuật số B-52D. Nó cũng được lắp đặt trên máy bay ném bom B-52G/H như một phần của Hệ thống điện tử tấn công. AP-101C được thiết kế để chống chọi với các mối nguy hiểm về bức xạ và xung điện từ (EMP), với các mạch được làm cứng bằng bức xạ và tính chẵn lẻ trong bộ nhớ. Tính năng "vượt vòng hạt nhân" của nó hoạt động trở lại sau 50 mili giây sau một sự kiện hạt nhân, có lẽ đã phát hiện ra một vụ nổ hạt nhân và nhanh chóng khởi động lại để tránh những tác động có hại như chốt.

Máy tính AP-101C. Từ tài liệu quảng cáo "IBM Model AP-101C", được chỉnh sửa lại vào tháng 9 năm 1978.

AP-101C khởi đầu Dòng máy tính mô-đun,19 sử dụng các trang 9"×6,4", lớn hơn nhiều so với các trang trước. Các trang MCS đã được mô-đun hóa, hỗ trợ các mô-đun tiêu chuẩn cho CPU, bộ nhớ, thời gian, nguồn điện, kiểm tra và xe buýt nối tiếp quân sự mới có tên MIL-STD-1553A. Trong khi các máy tính trước đó được tùy chỉnh bằng cách thay đổi vi mã trong Cửa hàng chỉ đọc (ROS) dựa trên lõi, thì AP-101C có thể được tùy chỉnh bằng cách thay đổi PROM (Bộ nhớ chỉ đọc có thể lập trình) và PLA (Bộ nhớ logic có thể lập trình) Mảng).

Một tập hợp trang Dòng máy tính mô-đun (MCS). Trang này là từ máy tính AWACS, Từ tài liệu quảng cáo "Hệ thống con xử lý dữ liệu AWACS", 1991.

Vào giữa những năm 1970, Không quân nhận ra rằng chi phí phát triển phần mềm cho các hệ thống quân sự phức tạp là một vấn đề, một phần vì các máy tính khác nhau có tập lệnh không tương thích. Để giải quyết vấn đề này, Không quân đã phát triển một bộ hướng dẫn và kiến trúc 16-bit tiêu chuẩn, phát hành tiêu chuẩn có tên MIL-STD-1750A vào tháng 7 1980. Lực lượng Không quân đã quy định 1750A là bắt buộc đối với các dự án trong tương lai (trừ khi có lý do thuyết phục để không sử dụng nó), vì vậy nhiều công ty triển khai máy tính tương thích với 1750A. IBM đã phát triển một phiên bản AP-101 chạy tập lệnh 1750A và gọi nó là AP-101E.

AP-101F (1982) đã được đổi mới về nhiều mặt. Đó là một máy tính có kiến trúc kép có thể hỗ trợ cả AP-101 hiện có. tập lệnh (MMP) và tập lệnh tiêu chuẩn 1750A, cung cấp đường dẫn nâng cấp có rủi ro thấp. Nó nhanh hơn nhiều, sử dụng kiến trúc đường ống chạy hơn 1 triệu lệnh mỗi giây (MIPS). AP-101F cũng sử dụng bộ nhớ bán dẫn DRAM (RAM động), nhanh hơn, dày đặc hơn và sử dụng ít năng lượng hơn so với AP-101F. bộ nhớ lõi.20

Việc chọn bộ nhớ bán dẫn thay vì bộ nhớ lõi có vẻ như là một lựa chọn hiển nhiên, nhưng bộ nhớ lõi từ có hai ưu điểm đáng kể. Đầu tiên, bộ nhớ lõi không khả biến: nó giữ nội dung của nó khi tắt nguồn, vì vậy các chương trình không cần phải tải khi khởi động. Thứ hai, bộ nhớ lõi có khả năng chống lại bức xạ hạt nhân và tia vũ trụ, những mối nguy hiểm có thể dễ dàng lật các bit trong bộ nhớ bán dẫn. Vấn đề biến động đã được giải quyết bằng cách cung cấp pin sao lưu cho bộ nhớ bán dẫn. AP-101F đã giải quyết vấn đề bức xạ bằng cách sử dụng bộ nhớ bán dẫn được hỗ trợ bởi bộ nhớ lõi "bóng". Các máy tính sau này sử dụng bộ nhớ bán dẫn với các mã sửa lỗi có thể phục hồi sau khi đảo bit: mỗi từ 16 bit trong bộ nhớ có thêm 6 bit để sửa lỗi.21 Do sự cân bằng, một số máy tính (chẳng hạn như ML-1 được thảo luận bên dưới) có thể sử dụng bộ nhớ lõi hoặc bộ nhớ bán dẫn, tùy thuộc vào ứng dụng.

Máy bay ném bom B-1B sử dụng tám máy tính AP-101F: mỗi máy tính dùng để hướng dẫn và dẫn đường, cung cấp vũ khí, điều khiển và hiển thị, dự phòng nhiệm vụ quan trọng, tiền xử lý và kiểm tra hệ thống (CITS), trong khi hai máy tính cung cấp thông tin địa hình sau đây. (xem Áp dụng tiêu chuẩn cho Chương trình điện tử hàng không B-1B ). Để giảm thiểu rủi ro về lịch trình, ban đầu B-1B sử dụng AP-101C từ B-52, sau đó chuyển sang AP-101D. Do nhu cầu về bộ xử lý mạnh hơn và áp lực phải sử dụng tập lệnh tiêu chuẩn 1750A, B-1B đã chuyển sang kiến trúc kép AP-101F, viết lại dần dần phần mềm từ hợp ngữ sang ngôn ngữ JOVIAL tiêu chuẩn.

Thiết kế lại tàu con thoi: AP-101S

Kẻ thù không đội trời chung của máy tính quân sự là Định luật Moore. Ngay cả khi bạn bắt đầu với một chiếc máy tính tiên tiến, có thể phải mất một thập kỷ để một chiếc máy bay được đưa vào sử dụng, và sau đó chiếc máy bay đó có thể được bay trong nhiều thập kỷ. Trong khi đó, máy tính thương mại trở nên mạnh mẽ hơn rất nhiều sau mỗi thập kỷ. Kết quả là các máy tính quân sự liên tục phải chống lại sự lỗi thời.

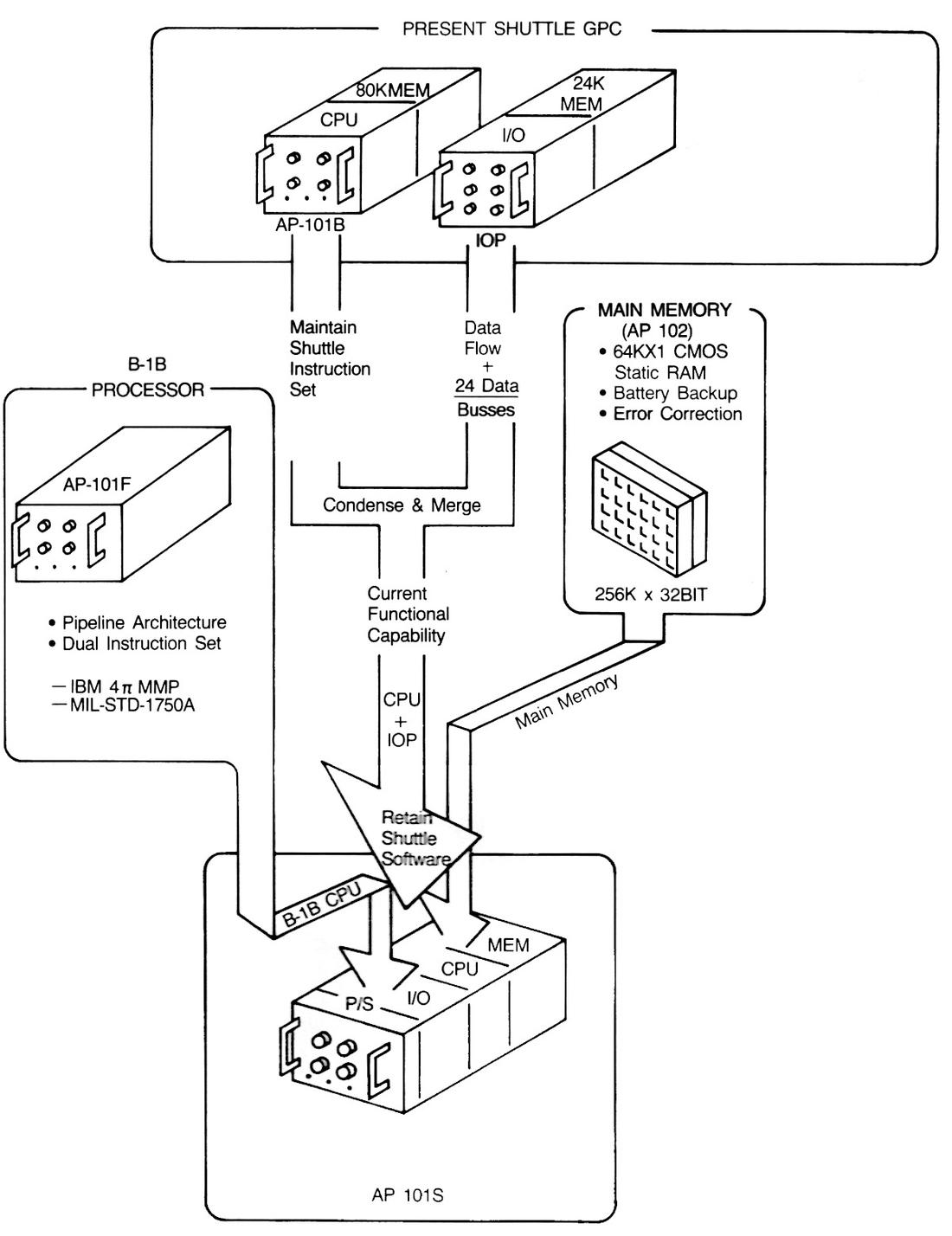

Máy tính không gian có cùng một vấn đề: Máy tính AP-101 của Shuttle được phát triển vào năm 1972 nhưng mãi đến năm 1981, Shuttle mới bay được, khiến máy tính Shuttle trở nên lỗi thời ngay từ đầu. Để cải thiện hiệu suất, IBM bắt đầu thiết kế lại máy tính vào năm sau, tạo ra AP-101S. Nó thực thi 1,27 triệu lệnh mỗi giây (MIPS), nhanh gấp ba lần so với AP-101B. Tuy nhiên, sự gia tăng hiệu suất này chẳng là gì so với những cải tiến trong các bộ vi xử lý. Năm 1991, khi AP-101S bay lần đầu tiên, bộ vi xử lý Motorola 68040 đã thực thi 44 MIPS, khiến AP-101S chìm trong bụi. Vào thời điểm chương trình Shuttle kết thúc vào năm 2011, bộ xử lý Intel Core i7 đã cung cấp tới 100.000 MIPS. Các phi hành gia phải sử dụng máy tính xách tay đến bù đắp cho sự thiếu hụt sức mạnh tính toán trong các máy tính chính; một chuyến bay mang theo 18 máy tính xách tay Thinkpad.

AP-101S đã được tháo nắp. Đây là một nguyên mẫu; các bảng màu xanh lá cây ở bên trái có thể là các bảng phát triển thay vì các bảng I/O thường ở những vị trí này.

Mặc dù không có hiệu suất tuyệt đối nhưng AP-101S là một cải tiến đáng kể so với máy tính Shuttle trước đó. AP-101S lắp chức năng của máy tính AP-101B và IOP (Bộ xử lý I/O) vào một hộp thay vì hai, tiết kiệm được 60 bảng. Với năm máy tính trên Shuttle, sự thay đổi này đã giải phóng 300 pound trọng tải. Ngoài tốc độ tăng gấp ba lần, AP-101S còn đáng tin cậy hơn, có bộ nhớ 256K từ thay vì 104K, và sử dụng ít hơn 100 watt so với công suất giới hạn của Tàu con thoi. AP-101S vẫn tương thích với máy tính cũ và có thể chạy cùng một phần mềm, giúp việc nâng cấp trở nên dễ dàng hơn. đơn giản.

Một trong các bo mạch CPU của AP-101S, cụ thể là bo mạch CPU1. Nếu nhìn kỹ, bạn có thể thấy "dây bodge" sửa lỗi trên bo mạch. Chín IC lớn ở giữa là các chip đơn vị logic số học bốn bit (74F181) cho ALU "phân số" 36 bit. Phần lớn logic sử dụng chip TTL FAST (Fairchild Advanced Schottky Technology) để cải thiện hiệu suất. Bảng được phủ một lớp phủ bảo giác màu nâu để bảo vệ nó khỏi môi trường. Nhấp vào hình ảnh này (hoặc bất kỳ hình ảnh nào khác) để xem phiên bản lớn hơn.

Giống như các bộ xử lý trước đó, CPU của AP-101S được xây dựng từ nhiều trang chip TTL. Không giống như AP-101B trước đó, AP-101S sử dụng các trang "MCS" lớn như minh họa ở trên. Sơ đồ bên dưới minh họa cách máy tính AP-101S nâng cấp được hình thành bằng cách kết hợp CPU theo đường dẫn 22 từ AP-101F hiệu suất cao, Bộ xử lý I/O từ máy tính Shuttle ban đầu và bộ nhớ bán dẫn từ AP-102 (được thảo luận trong phần tiếp theo).23

Đường dẫn nâng cấp cho máy tính Tàu con thoi. (Nhấp vào hình ảnh này (hoặc bất kỳ hình ảnh nào khác) để có phiên bản lớn hơn.) Từ "Máy tính mới cho tàu con thoi: Bản nâng cấp máy tính đa năng (GPC) AP-101S", Hướng dẫn kỹ thuật của IBM, 1986.

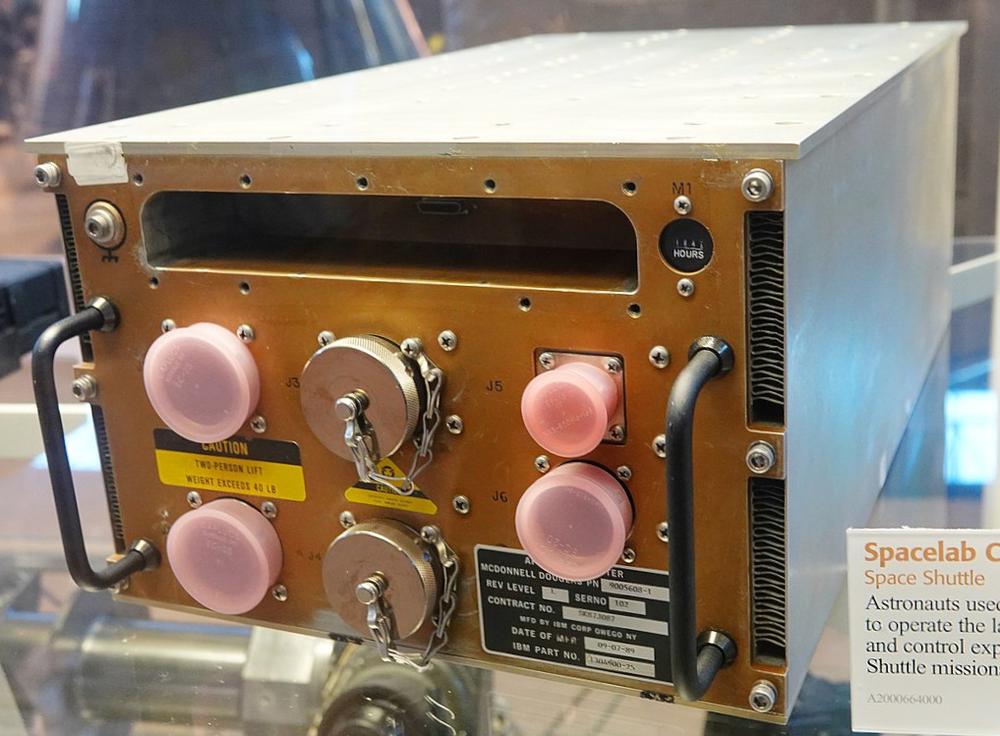

Tàu con thoi có thể chở một phòng thí nghiệm không gian có tên Spacelab (khác hoàn toàn với Skylab) trong khoang chở hàng để cung cấp một môi trường nghiên cứu rộng rãi. Spacelab có các máy tính độc lập với Tàu con thoi, ban đầu là máy tính CIMSA 125 MS do Pháp chế tạo.24 Năm 1991, những chiếc máy tính Spacelab này được được thay thế bằng máy tính IBM AP-101SL.25 AP-101SL tương thích với máy tính CIMSA 16 bit nên có thể chạy "Hệ điều hành máy tính thử nghiệm" và phần mềm Spacelab khác mà không cần thay đổi.

Một máy tính AP-101SL tại Bảo tàng Hàng không và Vũ trụ Quốc gia, VA. Khe ở phía trên chứa pin niken-cadmium để bảo quản nội dung của bộ nhớ CMOS, nhưng pin đã được tháo ra để đảm bảo an toàn trong quá trình bảo quản. Ảnh của Sanjay Acharya, CC BY-SA 4.0, đã cắt.

Bên trong, máy tính Spacelab AP-101SL rất giống với AP-101S của Shuttle. Nó có ít bo mạch hơn AP-101S, vì nó không bao gồm IOP (Bộ xử lý I/O) của Shuttle. Bo mạch xử lý, bộ nhớ bán dẫn26 và nguồn điện gần như giống hệt nhau với máy tính Shuttle, trong khi các bo mạch I/O thì khác.27

AP-101SL đã tháo nắp. Ảnh do Kyle Owen cung cấp.

AP-102 và VHSIC

Trở lại giữa những năm 1980, IBM giới thiệu máy tính AP-102. Đến năm 1992, nó đã trở thành phổ biến nhất bộ xử lý điện tử hàng không của IBM, với 1000 chiếc được bán ra. AP-102 là một bước nhảy công nghệ so với AP-101 vì nó sử dụng hai chip VLSI (Tích hợp quy mô rất lớn), mỗi chip chứa 12.000 cổng: một chip triển khai Bộ xử lý lệnh và chip còn lại triển khai Đơn vị số học mở rộng (cố định và nhân và chia dấu phẩy động). Những con chip này được triển khai với công nghệ 2 µm NMOS. AP-102 sử dụng CMOS tĩnh RAM để lưu trữ, dày đặc hơn nhiều so với bộ nhớ lõi và sử dụng 1/10 năng lượng. Vì RAM CMOS mất nội dung khi không có điện nên AP-102 đã sử dụng pin dự phòng, tế bào lithium thionyl clorua có thể cung cấp năng lượng cho bộ nhớ lên đến bảy năm.

Máy tính AP-102. Từ Chỉ dẫn Kỹ thuật của IBM, 1985 (bìa).

AP-102 nhỏ gọn, có chiều rộng bằng một nửa AP-101.28 Nó nặng 20,8 pound và sử dụng 95 watt. Nó chạy bộ lệnh 1750A tiêu chuẩn của Không quân, thực hiện hơn 1 triệu lệnh mỗi giây. AP-102 được sử dụng trên nhiều máy bay vào cuối những năm 1980, bao gồm máy bay chiến đấu tàng hình F-117A Nighthawk, trực thăng Chiến dịch Đặc biệt MH-53J, Hệ thống dẫn đường và cung cấp vũ khí của F-4 (AN/ASQ-203), một "tàu chiến không xác định" và một ứng dụng mật.

Vài năm sau, AP-102 được nâng cấp với công nghệ mới mang tên VHSIC. Nếu bạn đã lập trình một FPGA (Mảng cổng lập trình trường), có thể bạn đã sử dụng ngôn ngữ Verilog hoặc VHDL. VHDL hóa ra là từ viết tắt lồng nhau, viết tắt của Ngôn ngữ mô tả phần cứng VHSIC, trong đó VHSIC là viết tắt của Very High Speed Mạch tích hợp. Nhưng tại sao lại có cái tên lạ lùng này?

Năm 1980, Bộ Quốc phòng bắt đầu một chương trình trị giá hàng tỷ đô la để giúp quân đội Hoa Kỳ giữ vững vị trí dẫn đầu về công nghệ. Liên Xô. Chương trình này, chương trình Mạch tích hợp tốc độ rất cao, được thiết kế để đạt được các công nghệ tiên tiến, hiện đại nhất. mạch tích hợp được sử dụng trong quân sự nhanh hơn. IBM là một trong những nhà thầu đã phát triển các VHSIC này "siêu chip." IBM đã tạo ra bộ xử lý V1750, một con chip được làm cứng bằng bức xạ chạy bộ hướng dẫn tiêu chuẩn của Không quân, 1750A.29 Chip CMOS này được chế tạo với các tính năng 1 µm, tiên tiến vào thời điểm đó và chạy ở tốc độ 3 MIPS (triệu lệnh mỗi giây).

Máy tính nhiệm vụ AP-102 đã được được nâng cấp khoảng năm 1992 để sử dụng bộ xử lý V1750, dẫn đến AP-102A. Với bộ xử lý V1750, IBM lắp CPU và bộ nhớ vào một thẻ duy nhất, một sự thay thế có thể tháo rời cho sáu thẻ trong AP-102 hiện có. Kết quả là bộ nhớ tăng gấp 16 lần và hiệu suất được cải thiện gấp 3 lần, cùng với sự cải thiện về độ tin cậy, trọng lượng và mức tiêu thụ điện năng.

Bộ xử lý hệ thống con (SP)

Thành viên tiếp theo của dòng Hệ thống nâng cao là Bộ xử lý hệ thống con SP, dự định là một hệ thống con trong một hệ thống lớn hơn. So với dòng AP, máy tính SP có word 16 bit thay vì word 32 bit và nhìn chung nhỏ hơn và chậm hơn nhưng sử dụng ít năng lượng hơn. Máy tính SP có kiến trúc đơn giản hơn, chỉ có hai hoặc ba thanh ghi.

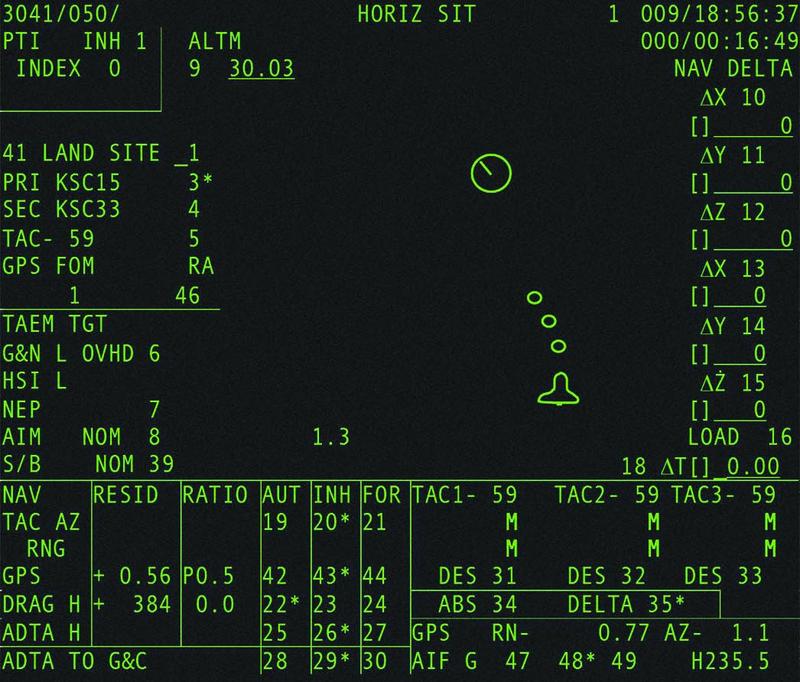

Trên Tàu con thoi, các phi hành gia nhận được thông tin chuyến bay và điều khiển qua 4 màn hình 30 Những màn hình CRT màu xanh lá cây đơn sắc này hiển thị văn bản và đồ họa nguyên thủy sử dụng vectơ—các đường được vẽ trên CRT—thay vì sử dụng pixel. Mỗi màn hình được điều khiển bởi Đơn vị Điện tử Hiển thị (DEU).

Ba màn hình CRT của Tàu con thoi. (Nhấp để xem hình ảnh lớn hơn.) Màn hình bên trái hiển thị Chỉ tay phổ quát thể hiện thái độ. Màn hình bên phải hiển thị Điều hướng tương đối màn hình cho các hoạt động điểm hẹn. Ở dưới cùng của bức ảnh là hai bàn phím kiểu lưới để giao tiếp với máy tính, với các nút điều khiển CRT ở giữa. Hai chiếc máy tính xách tay đang đặt trên bàn điều khiển. Phi công sứ mệnh Kevin Chilton ngồi ở ghế phi công. Từ Cục Lưu trữ Quốc gia.

Bên trong, DEU trông rất giống máy tính AP-101B của Shuttle, một chiếc hộp lớn chứa đầy các trang nhỏ. Một trong các trang là CPU của máy tính SP-0, trong khi các trang khác cung cấp bộ nhớ 32K từ, giao tiếp với các máy tính chính, và lái chiếc CRT. SP-0 xử lý việc lọc dữ liệu bàn phím, duy trì thời gian và tình trạng giám sát. SP-0 nhận dữ liệu động từ máy tính chính của Shuttle và định dạng dữ liệu cho màn hình CRT.

Bộ phận Điện tử Hiển thị Tàu con thoi (DEU). Đây là một nguyên mẫu kỹ thuật. Hình ảnh được cung cấp bởi Đấu giá RR.

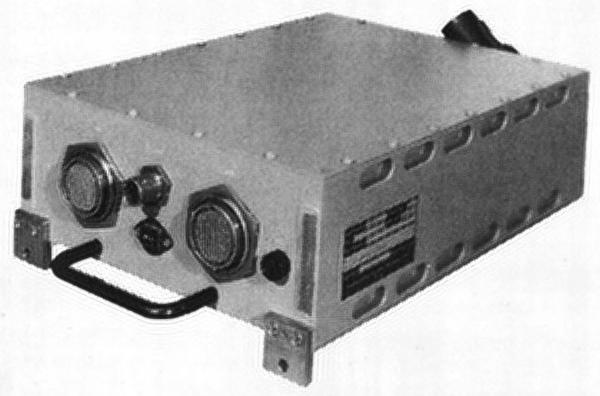

Máy tính SP-0A bên dưới có thể được sử dụng trong máy bay chống ngầm Lockheed S-3 Viking để phát hiện tín hiệu liên lạc và radar của đối phương trong hệ thống Biện pháp hỗ trợ điện tử AN/ALR-47.

Máy tính SP-0A. Từ tài liệu quảng cáo "Hệ thống IBM/4 Pi và Hệ thống nâng cao/Máy tính 4 Pi", tháng 8 năm 1973.

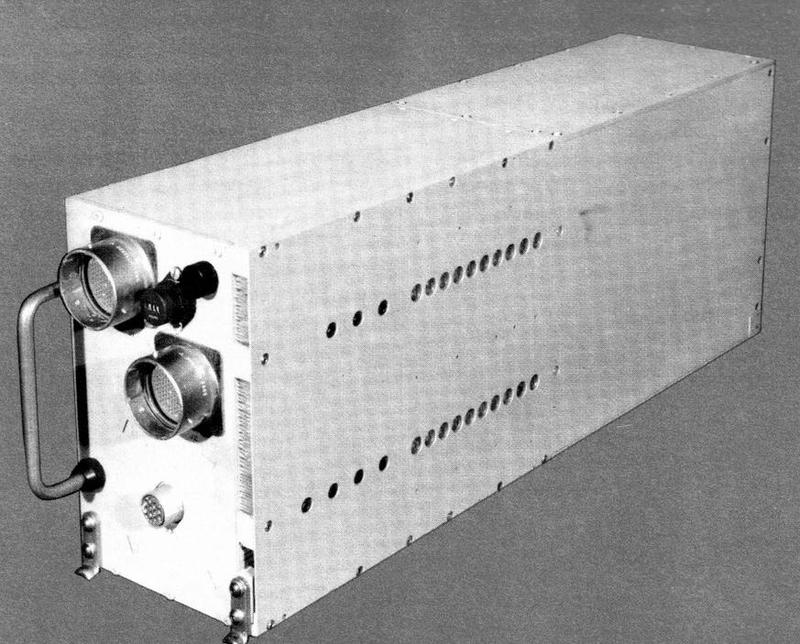

Máy tính SP-0B được sử dụng trong Đơn vị hướng dẫn giữa chặng cho tên lửa chống hạm Harpoon.31 Ban đầu nó có bộ nhớ lõi từ, được nâng cấp lên bộ nhớ bán dẫn vào năm 1974. Hãy chú ý đến bao bì cong của SP-0B giúp nó nằm gọn trong tên lửa.

Máy tính SP-0B. Từ tài liệu quảng cáo "Hệ thống IBM/4 Pi và Hệ thống nâng cao/Máy tính 4 Pi", tháng 8 năm 1973.

SP-1 bên dưới có nhiều thanh ghi hơn SP-0 cũng như hiệu suất cao hơn, chạy 342.500 thao tác mỗi giây. Nó cũng có sẵn dưới dạng SP-1A không đóng gói, chỉ nặng 3,6 pound. SP-1M đã thêm một số hướng dẫn để cải thiện hiệu suất. SP-1B lớn hơn nhiều, nặng 200 pound và được thiết kế để sử dụng trên mặt đất. IBM đưa ra một danh sách dài các ứng dụng cho SP-1: "F-4 ATIS, điều hướng, ổn định và điều khiển tên lửa và máy bay không người lái, bộ xử lý thông tin liên lạc, ổn định và kiểm soát ngư lôi."

Máy tính SP-1. Từ tài liệu quảng cáo "Hệ thống IBM/4 Pi và Hệ thống nâng cao/Máy tính 4 Pi", tháng 8 năm 1973.

Chiếc máy tính SP-201 cồng kềnh là một ngoại lệ so với những chiếc máy tính còn lại của dòng SP vì nó nặng tới 660 pound. Hiệu suất của nó cao hơn các mẫu SP khác, chạy 450.000 lệnh mỗi giây. Máy tính này là một phần của hệ thống sonar được sử dụng ở Los Angeles và Ohio lớp tàu ngầm. Mũi tàu ngầm chứa một quả cầu khổng lồ, đường kính 15 feet, được gắn hơn một nghìn bộ chuyển đổi để phát hiện âm thanh dưới nước. SP-201 là "bộ xử lý tín hiệu sau phân loại"32 trong AN/BQQ-5, phân tích những tín hiệu sonar này và việc lái xe cuộn "thác nước" hiển thị với các đường màu xanh lục cho biết sự hiện diện của tàu (hoặc đôi khi là cá voi). Chiếc máy tính này được thiết kế cẩn thận để hạ xuống qua cửa sập 25 inch tiêu chuẩn của tàu ngầm.

Máy tính SP-201, được chỉ định CP-1125/BQQ-5. Từ tài liệu quảng cáo "Hệ thống IBM/4 Pi và Hệ thống nâng cao/Máy tính 4 Pi", tháng 8 năm 1973.

Lệnh và Kiểm soát (CC)

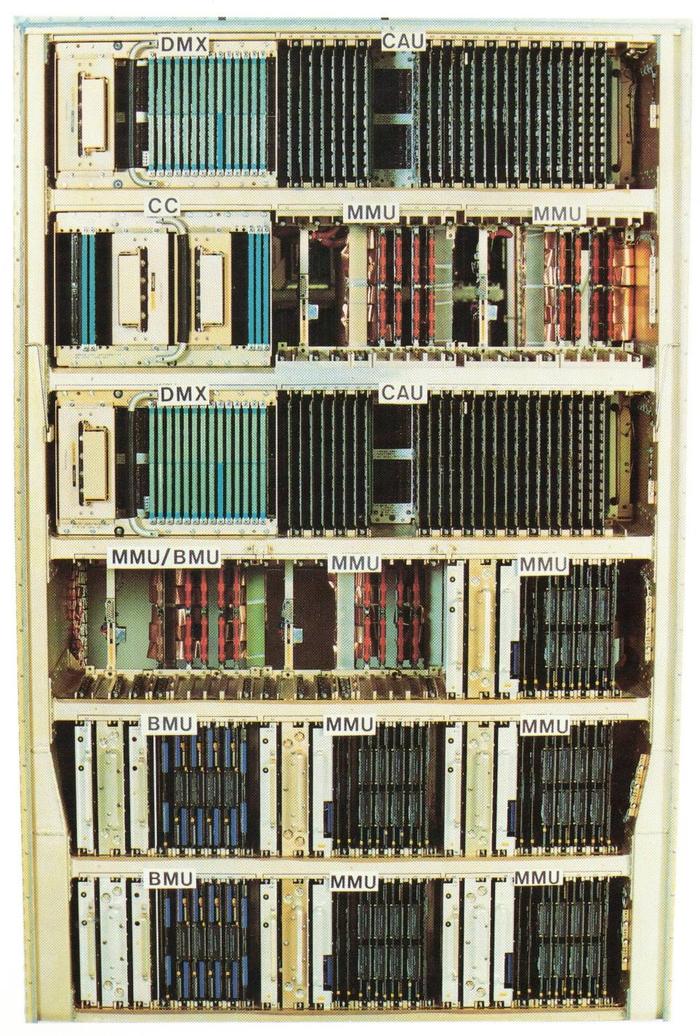

Mặc dù dòng AP là ngôi sao của dòng Advanced System/4 Pi, nhưng các máy tính CC lớn đã chạy Máy bay Boeing E-3A Sentry AWACS (Hệ thống điều khiển và cảnh báo trên không). AWACS là một chiếc Boeing 707 với mái vòm radar xoay cao 30 foot phía trên, trông như thể một cây nấm khổng lồ mọc ra từ thân máy bay. Radar này đã theo dõi hoạt động cách đó hơn 250 dặm, cung cấp cái nhìn toàn diện về chiến trường. Bên trong AWACS, CC là máy tính nhiệm vụ trung tâm, xử lý dữ liệu radar và gửi nó đến 14 thiết bị đầu cuối hiển thị. như cung cấp các chức năng chỉ huy và kiểm soát.

CC-1 được phát triển vào năm 1971 với tư cách là sản phẩm có hiệu suất cao nhất của dòng System/4 Pi với tốc độ 740.000 thao tác mỗi giây. Nó hỗ trợ kiến trúc System/360—bao gồm các thiết bị ngoại vi System/360—nhưng cũng hỗ trợ "kiến trúc CC-1" được tối ưu hóa.33 Tiếp theo CC-1 là CC-2 (1980), nâng hiệu suất lên 2 triệu lệnh mỗi giây thông qua việc sử dụng Siêu Schottky TTL.

Máy tính CC-2E với tính năng Tăng cường bộ nhớ cung cấp dung lượng lưu trữ chính gấp bốn lần và gấp tám lần dung lượng lưu trữ số lượng lớn. CC-2E rất lớn so với phần còn lại của dòng 4 Pi, nặng 1826 pound và cao gần 6 feet. Nó chạy hơn 2,7 MIPS (Triệu lệnh mỗi giây), nhanh hơn gấp đôi tốc độ của máy tính nâng cấp của Tàu con thoi. Máy tính được dự phòng để đảm bảo độ tin cậy. Nó cũng bao gồm "phát hiện sự kiện hạt nhân và khả năng sống sót".

Cấu hình cơ bản cho máy tính kỹ thuật số AWACS CC-2E. Các thành phần là Bộ ghép kênh kỹ thuật số (DMX), Bộ số học máy tính (CAU), Điều khiển máy tính (CC), Đơn vị bộ nhớ nguyên khối (MMU), và Bộ nhớ bong bóng (BMU). Từ tài liệu "Hệ thống con xử lý dữ liệu AWACS", 1991.

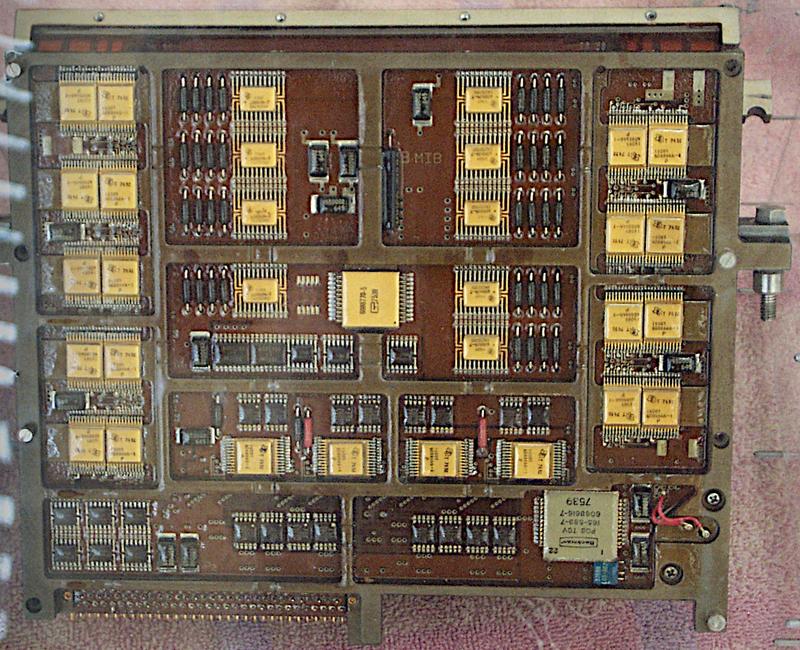

Ảnh trên cho thấy tủ có kích thước bằng tủ lạnh của CC-2E. Máy tính được cấu tạo từ hai loại bo mạch: hầu hết hệ thống đều sử dụng các trang MCS lớn, trong khi các đơn vị DMX và Điều khiển máy tính đã sử dụng các trang squat của hệ thống 4 Pi trước đó.

CC-2E đã sử dụng một công nghệ đặc biệt để lưu trữ hàng loạt không biến đổi: bộ nhớ bong bóng. Vào những năm 1970, bộ nhớ bong bóng là công nghệ lưu trữ của tương lai, cung cấp dung lượng đĩa cứng ở tốc độ bộ nhớ lõi. Nó sử dụng những "bong bóng" từ tính nhỏ di chuyển dọc theo đường ray bằng từ trường. Tuy nhiên, những cải tiến về bộ nhớ bán dẫn đã khiến bộ nhớ bong bóng trở nên kém cạnh tranh; đến năm 1981, tờ New York Times đã nhắc đến một cách mỉa mai tới Bong bóng máy tính vỡ. Bộ nhớ bong bóng được quân đội ưa chuộng vì nó không nhạy cảm với các rung động, không giống như đĩa cứng. Mỗi đơn vị bộ nhớ bong bóng (BMU trong ảnh) trong CC-2E lưu trữ 8 megabyte, gấp bốn lần so với đơn vị bộ nhớ nguyên khối dựa trên chất bán dẫn (MMU) có kích thước tương tự. Chúng thay thế bốn trống từ quay trong bản gốc CC-1, mỗi bản lưu trữ 400.000 từ. Để bảo vệ thông tin không rơi vào tay kẻ xấu, mô-đun bộ nhớ bong bóng có tính năng "hủy dữ liệu".

Bộ đơn vị số học máy tính, một trong hai bộ trong máy tính AWACS. Từ tài liệu "Hệ thống con xử lý dữ liệu AWACS", 1991.

CC-2E có hai đơn vị số học, mỗi đơn vị được xây dựng từ khoảng 26 trang MCS (ở trên). Mỗi đơn vị số học là một máy tính 32 bit thực hiện 182 lệnh dấu phẩy động và dấu phẩy cố định và có bộ đệm 8K từ để thực hiện. Nó tương thích với máy tính lớn System/360 và có các tiện ích mở rộng như hỗ trợ các trường bit có độ dài tùy ý.

ML-1

Khoảng năm 1974, IBM giới thiệu máy tính ML-1 nhỏ gọn34 một nửa chiều rộng của AP-101. Tiến bộ công nghệ trong ML-1 là chip LSI (Tích hợp quy mô lớn), trung bình có 110 cổng logic trên mỗi chip. (LSI thường được định nghĩa là có 100-1000 cổng, vì vậy những chip này nằm ở mức rất thấp của LSI.) Mỗi con chip được gắn trên một đế gốm hình vuông, mỗi cạnh 1 inch, có 48 chân ở mặt dưới. 35

Máy tính IBM ML-1. Ngăn xếp bộ nhớ lõi có thể nhìn thấy ở bên phải. Từ một quảng cáo trên Tạp chí Không quân, tháng 4 năm 1975.

Máy tính ML-1 sử dụng bộ nhớ lõi mô-đun giống như AP-101, CC-1 và các hệ thống khác. ML-1 cũng hỗ trợ bộ nhớ bán dẫn, vốn không ổn định (tức là mất nội dung khi không có điện), nhưng chi phí "thấp hơn đáng kể" so với bộ nhớ lõi từ, nhanh hơn, nặng hơn 8 pound (đối với máy tính 32K từ), sử dụng ít năng lượng hơn và giảm chiều dài của máy tính thêm 7 inch.

Máy tính IBM ML-1. Từ tài liệu quảng cáo "Hệ thống nâng cao/Máy tính đa dụng Model 4 Pi Model ML-1", tháng 12 năm 1974. 1974.

ML-1 có kiến trúc tương tự AP-101, ngoại trừ việc nó sử dụng đường dẫn dữ liệu 16 bit thay vì 32. Nó thực hiện 550.000 thao tác mỗi giây, giống như AP-101. IBM đã nói rằng ML-1 "có thể thích ứng với nhiều ứng dụng khác nhau như cung cấp vũ khí dẫn đường và điều hướng, điều khiển chuyến bay kỹ thuật số và liên lạc." Để hỗ trợ các ứng dụng liên lạc, ML-1 có các hướng dẫn xử lý byte tùy chọn. ML-1 đã được sử dụng trong thiết bị đầu cuối cho Hệ thống phân phối thông tin chiến thuật chung (JTIDS), với tư cách là người điều khiển xe buýt trong cơ sở thử nghiệm của IBM và trong một máy mô phỏng hạ cánh máy bay. Hai năm sau, IBM sản xuất ML-0 kém mạnh mẽ hơn, được đề cập ngắn gọn tại đây.

Kết luận

Dòng máy tính IBM System/4 Pi được biết đến nhiều nhất với các máy tính Space Shuttle, nhưng dòng máy tính này chứa nhiều máy tính ít được biết đến hơn, từ SP-1A nặng 3,6 pound đến CC-2E nặng 1826 pound. Máy tính 4 Pi minh họa cho sự tiến bộ nhanh chóng của công nghệ máy tính, từ các mạch tích hợp TTL đơn giản, bộ nhớ lõi từ, và hàng nghìn lệnh mỗi giây vào cuối những năm 1960 với các chip CMOS phức tạp, bộ nhớ bán dẫn dày đặc và hàng triệu lệnh mỗi giây vào những năm 1980.

Dòng 4 Pi đột ngột kết thúc vào năm 1994.

Máy tính điện tử hàng không bán chạy nhất của IBM là AP-102, với 1.000 chiếc được bán ra.

Đây là một con số làm tròn so với hàng triệu PC và máy tính PS/2 mà IBM đã bán ra.

Vào tháng 12 năm 1994, IBM quyết định tập trung vào hoạt động kinh doanh chính và

Để biết thông tin cập nhật, hãy theo dõi tôi trên Bluesky (@righto.com), Mastodon (@ [email được bảo vệ]), hoặc RSS.

Phần ghi nhận: Cảm ơn W. Tracz rất nhiều vì đã cung cấp nhiều tài liệu. Nhờ có Kyle Owen, Đấu giá RR, Marcel, Alex1970-14, Steve Jurvetson, Sanjay Acharya , José Luis Briz Velasco, Rich Katz, và bitsavers cho ảnh.37

Ghi chú và tài liệu tham khảo

-

Thông báo AI: Bất chấp sự hiện diện của em dash, không có AI nào được sử dụng để viết bài viết này. Tuy nhiên, Google Tìm kiếm có một số bài viết hữu ích trong Tổng quan về AI, xen lẫn với những kết luận rất đáng nghi vấn. ↩

-

Mô tả này về System/4 Pi là từ Niên giám máy bay, 1970. ↩

-

Nếu bạn là người có sở thích điện tử ở một độ tuổi nhất định, có lẽ bạn đã sử dụng mạch tích hợp TTL dòng 7400 phổ biến. Dòng 5400 là phiên bản quân sự của dòng 7400, xử lý phạm vi nhiệt độ rộng hơn từ -55 đến 125 °C. Hệ thống System/4 Pi ban đầu được sử dụng Texas Instruments Series 2400 mạch tích hợp, một biến thể của dòng 5400 được xây dựng theo thông số kỹ thuật của IBM dành riêng cho dòng 4 Pi. ↩

-

Skylab đã sử dụng nhiều từ viết tắt. Đài quan sát kính thiên văn được gọi là Núi Kính thiên văn Apollo (ATM). Các máy tính này điều khiển Hệ thống Kiểm soát và Chỉ báo Thái độ Skylab (APCS). Mỗi máy tính TC-1, với nguồn điện hỗ trợ và giao diện I/O, được gọi là Máy tính kỹ thuật số gắn kính thiên văn Apollo (ATMDC). Để biết chi tiết về máy tính của Skylab và phần mềm của chúng, hãy xem

Máy tính trong chuyến bay vũ trụ: Trải nghiệm của NASA và Phát triển hệ thống máy tính không gian trên tàu . ↩ -

Thế hệ máy tính System/4 Pi đầu tiên sử dụng lõi hình xuyến 13/21 của IBM (đường kính trong 13 triệu và 21 triệu đường kính ngoài) làm bằng lithium niken ferrite. Những lõi này hoạt động trong phạm vi nhiệt độ rộng (-55 đến 100 oC), điều quan trọng là cho một máy tính quân sự. (Để so sánh, một số máy tính lớn của IBM, chẳng hạn như 7090 , giữ lõi trong bồn dầu nóng để giữ nhiệt độ không đổi.) Những mặt phẳng lõi này là phiên bản quân sự hóa của các mặt phẳng lõi được sử dụng trong các mẫu System/360 cao cấp 65, 75 và 95. Một mặt phẳng lõi chứa 16.384 bit và mất 2,5 µs cho một chu kỳ truy cập. (Một số mặt phẳng lõi của IBM có thêm 512 bit, được gọi là bộ lưu trữ "vết sưng". Kết quả là loạt EP có dung lượng lưu trữ là 8448 từ thay vì dự kiến là 8192.) ↩

-

CP có nghĩa là gì? Tài liệu IBM ban đầu nói rằng CP là viết tắt của "Hiệu suất chi phí" nhưng hầu hết các nguồn khác đều sử dụng "Bộ xử lý tùy chỉnh". Một Bài báo Điện tử năm 1966 nêu cả hai tên này. ↩

-

Các bit bảo vệ lưu trữ cho phép một từ trong bộ nhớ lõi được đánh dấu là chỉ đọc. Vì bộ nhớ lõi bảo toàn nội dung của nó ngay cả khi không có nguồn điện nên phần mềm thường được ghi vào bộ nhớ lõi khi hệ thống đã được thiết lập và sau đó dữ liệu vẫn tồn tại. Tuy nhiên, nếu phần mềm bị hỏng trong bộ nhớ lõi thì không có cách nào dễ dàng để tải lại nó. Do đó, các bit bảo vệ lưu trữ có vai trò quan trọng trong việc bảo vệ phần mềm khỏi các sự cố vô tình. writes. ↩

-

Vi mã được lưu trữ trong một ROM, được gọi là Bộ lưu trữ chỉ đọc (ROS) theo thuật ngữ của IBM. Bộ lưu trữ chỉ đọc được triển khai bởi các mặt phẳng bộ nhớ lõi trong đó lõi hiện diện ở bit 1 và bị bỏ qua ở bit 0. Điều này khác với bộ nhớ dây lõi của Máy tính Hướng dẫn Apollo, vốn lưu trữ 192 bit trên mỗi lõi bằng cách truyền dây qua lõi hoặc xung quanh lõi. Các lõi ROS nhỏ hơn nhiều so với các lõi bộ nhớ chính, 7/12 so với 13/21 (đường kính trong và đường kính ngoài tính bằng mil). ↩

-

Hệ thống chỉ định "AN" trước đây được gọi là Hệ thống danh pháp liên hợp lục quân-hải quân, nhưng bây giờ là Hệ thống chỉ định loại điện tử chung ( chi tiết). Ví dụ: trong ký hiệu máy tính TC-2, "CP-952" chỉ ra rằng thiết bị này là máy tính, model 952. Máy tính này là một phần của hệ thống máy tính dẫn đường/cung cấp vũ khí "ASN-91(V)", trong đó "A" dành cho Máy bay được thí điểm, "S" dành cho Máy bay đặc biệt, "N" dành cho Hỗ trợ điều hướng và "V" dành cho biến thể. Do đó, các mã gồm ba chữ cái khó hiểu xác định chi tiết loại hệ thống.

↩ -

Điều gây tò mò là hệ thống 4 Pi ban đầu (TC, CP và EP) có sự khác biệt hoàn toàn tập lệnh và triển khai phần cứng. Từng làm việc tại Sun Microsystems, tôi nghi ngờ rằng các nhóm cạnh tranh bên trong IBM sản xuất các sản phẩm khác nhau vì lý do chính trị, để việc tiếp thị giả vờ rằng các sản phẩm hình thành một kế hoạch mạch lạc.

↩ -

Các máy tính trong dòng IBM System/360 có số kiểu máy hợp lý: khi số kiểu máy tăng lên, máy tính mạnh hơn và đắt hơn. Model 20 ở mức thấp, sau đó số lượng mẫu tăng lên (khoảng theo bước 10) đến Model 91, với bước nhảy vọt về số lượng lên Model 195.

Đối với thị trường tính toán khoa học, Model 44 là "một chiếc máy tính có hiệu suất gần 360/50 với mức giá 360/30" (tham khảo). Để đạt được điều này, IBM đã thực hiện một số thay đổi đối với kiến trúc 360 tiêu chuẩn. Cụ thể, Model 44 đã bỏ đi 19 hướng dẫn định hướng kinh doanh và thêm vào các tính năng như dấu phẩy động có độ chính xác thay đổi. Model 44 cũng bổ sung các hướng dẫn và ngắt ưu tiên để hỗ trợ thu thập dữ liệu theo thời gian thực cho các ứng dụng khoa học. Hệ thống System/4 Pi EP cũng xử lý dữ liệu thời gian thực—mặc dù dành cho ứng dụng quân sự chứ không phải khoa học—vì vậy dựa trên EP trên Model 44 là một lựa chọn hợp lý. ↩

-

Bảng dưới đây tóm tắt dòng máy tính AP của IBM.

1970 AP-1 F-15 Bộ nhớ lõi từ 8K

→ ISA điểm cố định1972 AP-101 Xe đưa đón Được lập trình vi mô

→ Dấu phẩy động thập lục phân

→ Bộ nhớ lõi từ 16K1976 AP-101B B-52D → Bộ nhớ lõi 32k từ

→ Dấu phẩy động nhị phân1978 AP-101C B-52G/H • Các chức năng đặc biệt được vi mã hóa

$ MIL-STD-1553A

→ Công nghệ MSI và LSI1981 AP-101D B-1B Bộ nhớ lõi từ 64K

→ SỮA-STD- 1553B1981 AP-101E SEAFAC ISA MIL-STD-1750A

→ Chứng nhận SEAFAC1982 AP-101F B- 1B → Kiến trúc kép (IBM và MIL-STD-1750)

à 4 1553B

• Bộ nhớ DRAM

> Hiệu suất 1 MIPS1983 AP-1R F-15 $ ISA điểm cố định, có thể chuyển đổi sang MIL-STD- 1750A

> Hiệu suất 1 MIPS1985 AP-102 Nhiều chương trình → ½ ATR

→ CPU SRU đơn

$ MIL-STD-1750A

> Hiệu suất 1 MIPS

→ Công nghệ VLSIBảng này từ AP-102: Áp dụng VLSI cho kiến trúc tập lệnh tiêu chuẩn của Không quân, Hướng dẫn Kỹ thuật của IBM 1985. Tôi không hoàn toàn tin tưởng vào bảng này vì các nguồn khác nói rằng Tàu con thoi sử dụng AP-101B và B-52D sử dụng AP-101C. Bảng này cũng cho biết rằng AP-101B sử dụng dấu phẩy động nhị phân, không khớp với các nguồn khác. SEAFAC đề cập đến Phòng thí nghiệm SEAFAC (Cơ sở kỹ thuật hệ thống điện tử hàng không) của Không quân, nơi được chứng nhận máy tính đáp ứng tiêu chuẩn 1750A. ↩

-

Tập lệnh được sử dụng trong AP-101 được gọi là MMP, viết tắt của Bộ xử lý đường giữa đa năng. Ngoại trừ tài liệu quảng cáo của IBM "Máy tính mục đích chung hệ thống tiên tiến/4 Pi Model ML-1" (1974) nói rằng nó là viết tắt của "bộ xử lý vi lập trình". Và bài viết “Một máy tính mới cho tàu con thoi” trong Hướng dẫn kỹ thuật của IBM (1986) nói rằng nó là viết tắt của Medium Multi-Purpose. Tôi tin rằng đây là những sai sót.

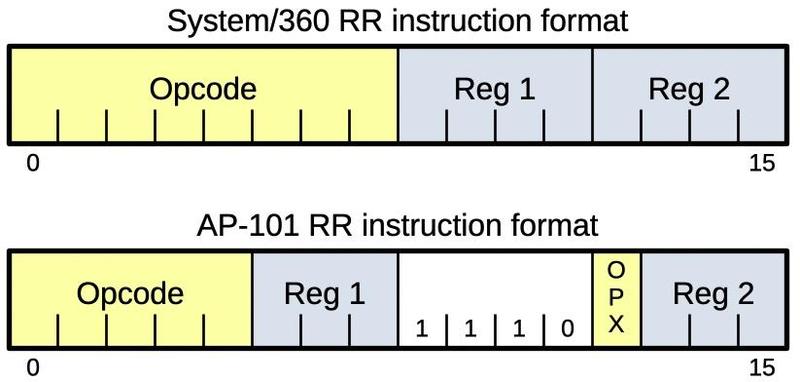

Tập lệnh MMP rất gần với tập lệnh System/360 ở cấp mã hợp ngữ; cái các hướng dẫn hầu hết đều giống nhau với cùng cách ghi nhớ. Không có gì ngạc nhiên khi MMP bỏ định hướng kinh doanh các lệnh như chuỗi có độ dài thay đổi và số học thập phân. MMP cũng cung cấp nhiều chế độ đánh địa chỉ nâng cao hơn System/360, bao gồm cả việc đánh địa chỉ gián tiếp.

Tuy nhiên, có nhiều thay đổi về cách triển khai khiến các máy tính hoàn toàn không tương thích ở cấp độ mã máy. Thay đổi đáng ngạc nhiên nhất là MMP hoàn toàn không sử dụng byte; một địa chỉ bộ nhớ truy cập vào một "nửa từ" 16 bit. Để so sánh, chính System/360 đã làm cho byte trở nên phổ biến. Các thanh ghi không tương thích: System/360 có 16 thanh ghi 32-bit đa năng, trong khi MMP có hai bộ tám thanh ghi. Hơn nữa, System/360 sử dụng địa chỉ 24 bit, hỗ trợ bộ nhớ 16 megabyte. MMP sử dụng địa chỉ 16 bit, được mở rộng lên 19 bit thông qua lựa chọn ngân hàng, chỉ hỗ trợ nửa từ 512K.

So sánh định dạng lệnh System/360 và MMP cho hướng dẫn đăng ký.

Sơ đồ trên cho thấy các lệnh mã hóa System/360 và MMP theo những cách hoàn toàn khác nhau. Cả hai hệ thống đều sử dụng định dạng lệnh "RR", chẳng hạn để thêm hai thanh ghi. Nhưng các lệnh 16 bit được mã hóa với cấu trúc hoàn toàn khác. Đặc biệt, MMP sử dụng ba bit thay vì bốn để chỉ định một thanh ghi, cùng với một mã rút gọn trường opcode.

Do có các tập lệnh tương tự nhau nên một lập trình viên ngôn ngữ hợp ngữ System/360 rất dễ dàng thực hiện bắt đầu lập trình dòng AP. Tuy nhiên, do không tương thích nên các chương trình MMP không thể chạy trực tiếp trên System/360 mà cần phải thực hiện thông qua một chương trình mô phỏng chức năng. Ngược lại, System/4 Pi EP trước đó tương thích với System/360, vì vậy các chương trình có thể chạy trực tiếp trên một trong hai máy.

↩ -

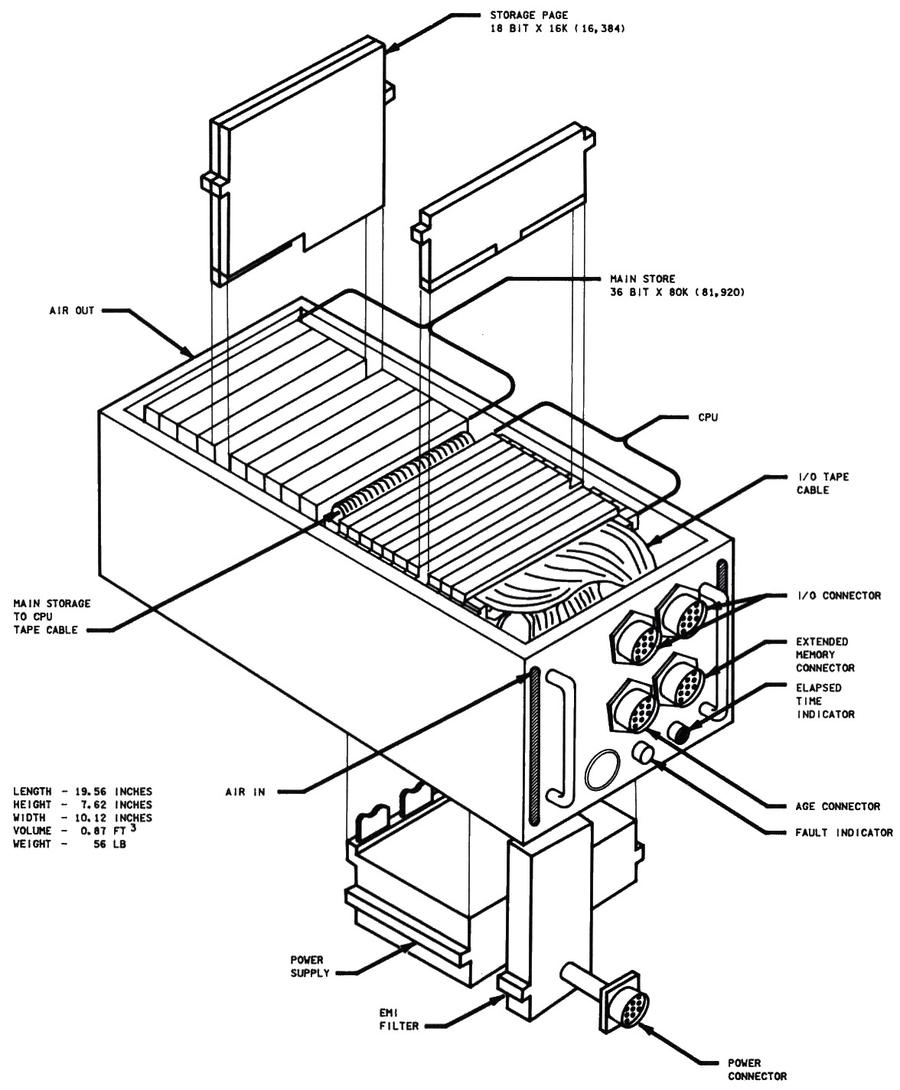

Hình vẽ bên dưới thể hiện hình ảnh chi tiết của CPU tàu con thoi AP-101B (tức là phiên bản cũ hơn). Một nửa hộp bị chiếm giữ bởi các trang lưu trữ lớn. Logic được triển khai với các trang Hệ thống/4 Pi ngồi xổm tiêu chuẩn, với nguồn điện bên dưới. Các đầu nối tròn ở mặt trước được kết nối với các trang thông qua các mạch in polyimide linh hoạt, một công nghệ ấn tượng vào những năm 1970. Chức năng của từng trang được mô tả trong

Hệ thống nâng cao của tàu con thoi/4 Bộ xử lý trung tâm Pi Model AP-101, trang 131 (6-11). -

Sự dư thừa của máy tính Tàu con thoi rất quan trọng trong chuyến bay STS-9A (1983). Tàu con thoi gặp phải hai lỗi máy tính khoảng năm giờ trước khi chuyến bay dự kiến diễn ra đất. GPC-1 (Máy tính đa năng 1) bị lỗi và không thể đưa trực tuyến trở lại. Sáu phút sau, GPC-2 cũng thất bại nhưng đã được đưa trở lại trực tuyến thành công (Báo cáo sứ mệnh STS-9, Tờ thông tin về Spacelab 1 ). Sự cố được cho là do một miếng hàn bị lỏng. Chỉ huy John Young mô tả tình hình: "Đầu gối của tôi bắt đầu run rẩy. Khi chiếc máy tính tiếp theo bị hỏng, Tôi chuyển sang thạch. Mắt của chúng tôi đã mở rộng hơn rất nhiều so với trước đây!" Bất chấp sự cố máy tính, IMU (đơn vị đo quán tính) bị lỗi và hai APU (bộ nguồn phụ) cháy , Tàu con thoi đã hạ cánh thành công. ↩

-

Điều kỳ lạ là AP-101B của Shuttle và IOP đã sử dụng các trang lưu trữ khác nhau: máy tính sử dụng các trang lưu trữ 16K×18, trong khi IOP sử dụng các trang lưu trữ 8K×18. Ban đầu, hệ thống được thiết kế cho tổng cộng 64K từ, sử dụng 16 trang 8K (nguồn , details ). Cuối cùng, máy tính đã sử dụng các trang 16K mật độ cao hơn, nhưng vì lý do nào đó, IOP vẫn sử dụng các trang 8K mật độ thấp hơn, dẫn đến tổng cộng 102K từ từ mười sáu trang, thay vì 128 nghìn từ mà bạn mong đợi. (Xem Sổ tay hệ thống tàu con thoi sơ đồ.) ↩

-

Hầu hết thông tin về AP-101C là từ tài liệu quảng cáo của IBM: "Dòng máy tính mô-đun hệ thống nâng cao IBM/4 Pi Model AP-101C". Bộ lệnh và kiến trúc AP-101C được mô tả trong tài liệu năm 1979 với tiêu đề Tàu con thoi - Model Nguyên tắc hoạt động của AP-101 C/M . Tiêu đề này gây khó hiểu vì Tàu con thoi sử dụng AP-101B và B-52 sử dụng AP-101C. Tài liệu nói một cách không rõ ràng rằng nó mô tả "AP-101C và AP-101, phiên bản nguyên khối". Sau đó, một tài liệu năm 1987, AP-101S với Bộ hướng dẫn đưa đón , cho biết AP-101S (máy tính Shuttle nâng cấp) tương thích phần mềm với AP-101C/M. Giả thuyết của tôi là IBM đã tạo nguyên mẫu AP-101C với bộ nhớ bán dẫn (nguyên khối) để nâng cấp Shuttle, nhưng đã bị bỏ rơi cách tiếp cận này. ↩

-

Máy tính System/4 Pi lật ngược các biểu diễn số dấu phẩy động. Các máy tính hiện đại sử dụng số mũ cơ sở 2 (nhị phân) cho dấu phẩy động, nhưng System/360 sử dụng số mũ cơ sở 16 (thập lục phân). (Sự khác biệt là bạn tăng 2 lên số mũ hay 16 lên số mũ.) Hệ thống EP đã sao chép biểu diễn System/360, nhưng sau đó AP-1 chuyển sang số mũ nhị phân. Sau đó AP-101 chuyển trở lại số mũ cơ số 16 (mặc dù một nguồn có thể sai nói rằng AP-101B đã sử dụng số mũ nhị phân). Hỗ trợ tập lệnh 1750A yêu cầu số mũ nhị phân, vì vậy các máy có kiến trúc kép hỗ trợ cả hai loại của số mũ. ↩

-

Các máy tính System/4 Pi sau này được gọi là MCS (Các dòng máy tính mô-đun khác nhau, Hệ thống máy tính mô-đun hoặc Dòng máy tính quân sự). Họ sử dụng lớn hơn bảng, được gọi là trang MCS, có kích thước 9"×6,4". Một trang MCS bao gồm hai bảng mạch in (được gọi là MIB, bảng kết nối nhiều lớp) được liên kết với nhau vào một tấm nhiệt kim loại giữa các bảng. Tấm nhiệt tiếp xúc với bộ trao đổi nhiệt của máy tính thông qua các ốc vít được gọi là khóa nêm cung cấp nhiệt. đường cho nhiệt thoát ra ngoài. Hệ thống này cho phép máy tính được làm mát bằng không khí đồng thời cách ly không khí làm mát khỏi các bộ phận.

↩ -

Tôi không tìm thấy ảnh của AP-101F nhưng bản vẽ đường cho thấy nó trông giống như AP-101C, với cách bố trí đầu nối giống nhau. Điều này hợp lý nếu AP-101F được chế tạo dưới dạng bản nâng cấp tương thích với phích cắm. ↩

-

Bộ nhớ lõi bóng trong AP-101F được đề cập trong Ứng dụng tiêu chuẩn cho Chương trình điện tử hàng không B-1B . Nó có 128K từ bộ nhớ lõi mô-đun mật độ cao (HMCM) che khuất 128K từ hoạt động bộ nhớ bán dẫn (SCM). Điều này kết hợp tốc độ và mức tiêu thụ điện năng thấp của bộ nhớ bán dẫn với khả năng chống bức xạ của bộ nhớ lõi từ.

Máy tính AP-101S của Shuttle đã sử dụng mã sửa lỗi (ECC) để khôi phục các bit bị lật trong trí nhớ. Mỗi nửa từ 16 bit có thêm sáu bit ECC (Mã sửa lỗi), cho phép sửa một bitflip trong một từ, trong khi hai bitflip có thể được phát hiện nhưng không được sửa chữa. Việc sửa lỗi được thực hiện bởi Am2960 chip. Một "máy chà" bộ nhớ sẽ quét bộ nhớ cứ sau 1,6789 giây để sửa bất kỳ bit nào bị đảo lộn. Hiện tượng lật bit do tia vũ trụ không phải là hiếm: có thể xảy ra hiện tượng lật bit hơn 100 bit trên một chuyến bay, nhưng chúng đã được sửa chữa trước khi gây ra sự cố. (chi tiết ). Trong một trường hợp, một tia vũ trụ gây ra lỗi 14 bit; cấu trúc của hệ thống bộ nhớ đảm bảo rằng những lỗi này ảnh hưởng đến một bit bằng 14 từ khác nhau, do đó không có lỗi bit kép và tất cả các lỗi đều có thể sửa được. Tuy nhiên, bộ nhớ thanh ghi trong CPU không được bảo vệ khỏi lỗi;

hai trục trặc máy tính được cho là do bức xạ. Bộ nhớ con thoi có các bit "bảo vệ lưu trữ" để đảm bảo mã không bị ghi đè (cũng như đảm bảo rằng dữ liệu không được thực thi). Một kỹ thuật khác đã được sử dụng để tránh làm hỏng các bit bảo vệ lưu trữ: Mỗi từ có ba bit bảo vệ lưu trữ và thuật toán biểu quyết xác định giá trị. ↩

-

Cấu trúc đường ống của AP-101S thực hiện lệnh theo sáu bước: dịch địa chỉ lệnh, tìm nạp lệnh, giải mã lệnh và tính toán địa chỉ bộ nhớ của toán hạng, dịch địa chỉ dữ liệu, tìm nạp toán hạng từ bộ nhớ và thực hiện lệnh. Nếu không có đường dẫn, một lệnh sẽ mất sáu chu kỳ để trải qua tất cả các giai đoạn này. Với hệ thống đường ống, ngay khi một lệnh hoàn thành một giai đoạn, lệnh tiếp theo có thể bắt đầu giai đoạn đó, vì vậy sáu lệnh có thể đồng thời hoạt động.

Việc tạo đường ống khiến bộ xử lý trở nên phức tạp hơn đáng kể. Hơn nữa, các yếu tố khác nhau làm giảm lợi ích hiệu suất, do đó tốc độ tăng tốc thấp hơn hệ số lý thuyết là sáu. Ví dụ: một chi nhánh đến một địa chỉ mới yêu cầu đường ống được khởi động lại với lệnh mới, lãng phí ba chu kỳ xung nhịp. Nếu như hai lệnh trong đường ống sửa đổi cùng một thanh ghi, một "nguy hiểm" có thể xảy ra, yêu cầu độ trễ trong đường ống để mỗi lệnh nhận được giá trị đăng ký chính xác. Một số lệnh mất nhiều hơn một chu kỳ cho giai đoạn thực thi, làm trì hoãn quy trình. Mã tự sửa đổi cũng có thể gây nguy hiểm nếu chương trình sửa đổi các hướng dẫn đã được tìm nạp trước. Trong trường hợp này, đường ống cần được khởi động lại để có được hướng dẫn chính xác được thực thi. Đường ống AP-101S được mô tả chi tiết trong Nguyên tắc hoạt động của mẫu tàu con thoi AP-101S với Bộ hướng dẫn tàu con thoi. ↩

-

Quá trình hình thành của AP-101S cũng được mô tả trong AP-101S với Bộ hướng dẫn tàu con thoi, phần 4. "Các thành phần được sử dụng từ AP-101F là CPU, MMU (Bộ quản lý bộ nhớ) và các phần Ngắt. Vi mã đã được sửa đổi để có thể sử dụng phần mềm tàu con thoi hiện có trên AP-101S. Trang Thời gian, trang SDI (Giao diện phát triển phần mềm) và bus SIB đã bị loại bỏ. Mạch không được sử dụng trong MMU đã bị loại bỏ để cho phép tích hợp các chức năng định thời và SDI vào MMU. IOP đã được đóng gói lại bằng cách sử dụng tích hợp quy mô trung bình để giảm số lượng trang từ 14 xuống còn 7." Sơ đồ chi tiết hơn về quá trình phát triển AP-101S có trong Máy tính đa năng AP101S (GPC) mới dành cho tàu con thoi. Điều kỳ lạ là nguồn tin đó khẳng định bộ nhớ trong AP-101S đến từ AP-101F chứ không phải AP-102. Nguồn này cũng giải thích về AP-101S/G, một phiên bản tạm thời được sử dụng trên mặt đất trong quá trình phát triển. AP-101S/G về cơ bản là AP-101S với IOP (Bộ xử lý I/O) của Shuttle là một hộp riêng biệt.

AP-101S của Shuttle có hỗ trợ bộ hướng dẫn tiêu chuẩn 1705A của Không quân cũng như bộ hướng dẫn MMP không? Nguồn là trái ngược nhau. AP-101F của B-1B hỗ trợ cả bộ hướng dẫn và AP-101S kế thừa kiến trúc này: "Bộ xử lý trung tâm AP-101S được tối ưu hóa cho cả MMP và MIL=-STD-1750A" (nguồn). Theo Máy tính đa năng AP101S (GPC) mới dành cho Tàu con thoi, bộ điều khiển bên trong và vi mã của AP-101S hỗ trợ cả hai kiến trúc và AP-101S có thể dễ dàng được cấu hình cho kiến trúc bằng tín hiệu điều khiển trên giao diện. Máy tính mặt đất AP-101SG/1750 ít người biết đến là đã nói đã chạy 1750A. Các nguồn khác nói rằng AP-101S không hỗ trợ 1750. Giải thích của tôi là mặc dù phần cứng của AP-101S hỗ trợ cả bộ hướng dẫn, phiên bản bay của AP-101S không có vi mã cho 1750A do không gian vi mã bị hạn chế. ↩

-

Spacelab ban đầu sử dụng máy tính CIMSA 125 MS. Việc đặt tên cho chiếc máy tính này rất khó hiểu. Bắt đầu từ năm 1971, một công ty của Pháp có tên CII đã sản xuất dòng máy tính mini 16-bit phổ biến có tên Mitra 15. Năm 1975, CII sản xuất mẫu kế nhiệm có tên Mitra 125. Vào giữa những năm 1970, CII và Honeywell sáp nhập và bộ phận máy tính được tách ra để thành lập SEMS, với cổ đông lớn là Thomson. Công ty con CIMSA của Thomson sản xuất máy tính cho Spacelab, máy tính 125 MS, một phần của dòng máy tính 15 M quân sự hóa của CIMSA. Máy tính này có chức năng giống với Mitra 125 S mà dự án Spacelab sử dụng trên mặt đất (chi tiết). Trong khi đó, MATRA (khác với Mitra) là nhà thầu cung cấp dữ liệu và chỉ huy Spacelab quản lý. Tóm lại, Spacelab đã sử dụng Máy tính CIMSA 125 MS, có thể được xác minh từ nhãn bên dưới. Đây là phiên bản quân sự hóa của Mitra 125, được sản xuất theo hợp đồng với MATRA. Đôi khi người ta gọi chiếc máy tính này là MATRA 125, nhưng đó lỗi.

Máy tính CIMSA 125 MS. Nhấp vào ảnh này (hoặc bất kỳ ảnh nào khác) để xem phiên bản lớn hơn. Ảnh của Steve Jurvetson, CC BY 2.0.

-

Vào năm 1990, lint đã gây ra lỗi máy tính gần như phá hỏng khả năng quan sát của Kính thiên văn chụp ảnh tia cực tím Astro trên chuyến bay Columbia (xem Tàu con thoi hạ cánh trong tình trạng tốt nhưng vẫn còn câu đố về xơ vải và Báo cáo sứ mệnh tàu con thoi STD-35 ). Cả hai thiết bị đầu cuối của Hệ thống hiển thị dữ liệu của Spacelab đều quá nóng và không hoạt động, kèm theo mùi cháy và chỉ số carbon monoxide cao (mặc dù kết quả chỉ số carbon monoxide sau đó được xác định là không hợp lệ). Các thiết bị đầu cuối bị lỗi là một phần của hệ thống máy tính do Pháp chế tạo ở Spacelab; Tôi không biết vấn đề này ảnh hưởng đến quyết định thay thế máy tính của Spacelab bằng AP-101SL của IBM như thế nào.

Tuy nhiên, máy tính của IBM không tránh khỏi các vấn đề làm mát do xơ vải gây ra. Một trong những Challenger máy tính quá nóng và hỏng trong quá trình thử nghiệm trên mặt đất vào năm 1984 sau khi đường dẫn khí của nó bị xơ vải làm tắc nghẽn (chi tiết). ↩

-

AP-101S có Bộ quản lý bộ nhớ (MMU), được triển khai trên hai trang. Trong hầu hết các máy tính, Đơn vị quản lý bộ nhớ thực hiện bộ nhớ ảo bằng cách dịch địa chỉ ảo sang địa chỉ vật lý, nhưng MMU trong AP-101S không tiên tiến bằng: MMU của nó đã mở rộng không gian địa chỉ bộ nhớ thông qua chuyển đổi ngân hàng.

Dòng máy tính AP-101 ban đầu sử dụng địa chỉ 16 bit truy cập các nửa từ 16 bit (không phải byte), để họ có thể truy cập trực tiếp các nửa từ 64K (tương đương 128 KB). Không đủ không gian địa chỉ cho phần mềm không ngừng phát triển, vì vậy AP-101B đã sử dụng cơ chế chuyển mạch ngân hàng kỹ thuật cho phép truy cập vào các nửa từ 512K, mặc dù ở dạng khối 32K. (AP-101B không thể chứa nhiều bộ nhớ bên trong như vậy nhưng có thể thêm hộp bộ nhớ ngoài.) Cụ thể, Từ trạng thái bộ xử lý chứa trường chọn ngân hàng 4 bit để truy cập mã và một trường 4 bit khác trường chọn ngân hàng để truy cập dữ liệu. Các trường này có thể được thay thế cho bit trên cùng, mở rộng không gian địa chỉ từ 16 bit đến 19 bit. AP-101S đã mở rộng phương pháp này bằng sơ đồ phức tạp của "Địa chỉ mở rộng". Theo cách tiếp cận này, mỗi thanh ghi chỉ mục có một trường chọn ngân hàng 4 bit riêng biệt. Điều này cho phép nhiều ngân hàng 32K được sử dụng cùng lúc.

Mục đích chính của Bộ quản lý bộ nhớ là chuyển đổi địa chỉ bộ nhớ 16 bit thành địa chỉ 19 bit địa chỉ bộ nhớ vật lý bằng cách thay thế các bit chọn ngân hàng thích hợp. MMU cũng phát hiện và xử lý các lỗi bộ nhớ. Cuối cùng, MMU bao gồm dường như ngẫu nhiên các chức năng như đồng hồ hệ thống 40 MHz của bộ xử lý.

(Đừng nhầm lẫn MMU (Bộ quản lý bộ nhớ) trong máy tính với MMU (Bộ nhớ chung), một trong hai ổ băng từ trên Shuttle; MMU (Đơn vị điều động có người lái), ba lô đẩy cho các cuộc đi bộ ngoài không gian; hoặc MMU (Đơn vị bộ nhớ nguyên khối), bộ nhớ bán dẫn của CC-2E) ↩

-

Từ trước ra sau, các bo mạch trong AP-101SL là: A4, A5, A6 (CPU3), A7 (CPU2), A8 (CPU1), A9 (ngắt), A10, A11, A12 (RAM), A13 (RAM), A14 (nguồn điện 12V) và A15 (nguồn điện 5V). A10 chứa bộ dao động 40 MHz, nằm trên bo mạch MMU2 trong AP-101S. Có lẽ A10 và A11 tương đương với bo mạch MMU, nhưng không có sơ đồ khối bộ nhớ đặc biệt của AP-101S. A4 có thể là bảng I/O kỹ thuật số. A5 có bộ cách ly quang và các thành phần tương tự, vì vậy nó có lẽ là một I/O bảng. Bộ nguồn và bảng nhớ trông giống hệt nhau giữa AP-101S của Shuttle và AP-101SL của Spacelab. Các trang CPU và ngắt rất giống nhau, có lẽ chỉ là sửa lỗi trong quá trình sự phát triển. Ngoại lệ là một mặt của trang CPU3 có sự khác biệt đáng kể. (Các bo mạch trong AP-101S được liệt kê trong AP-101S có bộ hướng dẫn Shuttle trang 18 nên tôi sẽ không lặp lại danh sách ở đây.) ↩

-

Bạn có thể nhận thấy rằng các máy tính System/4 Pi hầu hết trông giống nhau, các hộp hình chữ nhật có tay cầm và đầu nối ở mặt trước. Đó không phải là một sự trùng hợp ngẫu nhiên. Nhiều máy tính System/4 Pi có vỏ phù hợp với tiêu chuẩn ATR (Air Transport Rack), thường được sử dụng cho hệ thống điện tử hàng không. Hộp ATR tiêu chuẩn có chiều rộng khoảng 10,12" và cao 7,62" (nguồn). Độ sâu là 12,62" đối với hộp ngắn và 19,62" đối với hộp dài. Hộp 1/2 ATR tiêu chuẩn rộng 4,88" (nhỏ hơn một nửa chiều rộng của hộp đầy đủ do độ dày của giá đỡ giữ hộp). CP-1, CP-2, CP-3 và AP-101 có vỏ dài ATR, trong khi ML-1, SP-1 và AP-102 là 1/2 ATR. Các hệ thống khác, chẳng hạn như TC-2 và AP-1, không phù hợp với kích thước tiêu chuẩn.

↩ -

Các chip VHSIC dự kiến sẽ hoạt động trong môi trường có "mối đe dọa bức xạ hạt nhân và không gian" nên chúng đã được tăng cường chống lại sự phá hủy của bức xạ và xung điện từ (nguồn).

Bộ xử lý V1750 của IBM cũng được sử dụng trong máy tính trung tâm của máy bay F-15 (VCC, Máy tính trung tâm VHSIC), thay thế cho bộ xử lý V1750 của IBM. máy tính AP-1R trước đó vào khoảng năm 1992. Chip điều hòa tín hiệu VHSIC đã được sử dụng để cải tiến Bộ xử lý tín hiệu nâng cao vào giữa những năm 1980, giúp tăng gấp đôi hiệu suất của nó. Chương trình VHSIC cũng tài trợ cho "Máy tính không gian chung VHSIC" (GVSC) của IBM, được sử dụng trong tàu thăm dò không gian Cassini tới Sao Thổ và không gian khác. nhiệm vụ. (Thật khó hiểu, Bộ Quốc phòng đã tài trợ cho cả Honeywell và IBM để xây dựng Máy tính không gian VHSIC chung, vậy là có hai máy tính khác nhau có cùng tên.) Đến thời điểm này, IBM rõ ràng đã bỏ nhãn hiệu System/4 Pi, coi VHSIC là một nhãn hiệu thú vị hơn. ↩

-

Màn hình hiển thị của Tàu con thoi chứa nhiều văn bản nhưng bao gồm đồ họa vector, tiên tiến vào thời điểm đó. Màn hình bên dưới hiển thị Tàu con thoi đang chuẩn bị hạ cánh. Các vòng tròn nhỏ dự đoán vị trí của Tàu con thoi sau 20, 40 và 60 giây. Vòng tròn lớn biểu thị đường băng.

Màn hình của Tàu con thoi được mô tả bằng một mớ chữ viết tắt lộn xộn. Màn hình CRT là Đơn vị hiển thị (DU), một phần của Hệ thống hiển thị CRT đa chức năng (MCDS). Màn hình được điều khiển bởi Bộ phận điện tử hiển thị (DEU), chứa SP-0 bộ xử lý. SP-0 đã tạo Từ điều khiển định dạng (FCW) trong bộ nhớ để điều khiển các ký tự và vectơ trên màn hình. Năm 2000, MCDS được nâng cấp lên 11 màn hình LCD màu (MEDS). Để biết chi tiết, hãy xem Nâng cấp hệ thống điện tử hàng không của tàu con thoi: Các vấn đề và cơ hội, Sách hướng dẫn đăng ký, TAEM và Tiếp cận/Hạ cánh, Phần mềm chuyến bay tàu con thoi , Hệ thống điện tử hàng không của tàu con thoi, và Thiết kế hiển thị nâng cao của Tàu con thoi và Phân tích về Khả năng phát triển của nó . ↩

-

Một số nguồn nói rằng Tên lửa Harpoon sử dụng máy tính SP-0A, trong khi tài liệu quảng cáo của IBM nói rằng tên lửa sử dụng máy tính SP-0B. Có lẽ đã có một bản nâng cấp? ↩

-

Một Bài viết về IBM bao gồm một số bộ xử lý tín hiệu khác trong cuộc thảo luận về dòng IBM System/4 Pi. Các hệ thống chuyên biệt này thực hiện hàng chục triệu phép tính mỗi giây, nhanh hơn rất nhiều so với các hệ thống hiện đại. máy tính có mục đích chung. Tôi không chắc liệu chúng có được phân loại là hệ thống System/4 Pi "thực" hay không, vì vậy tôi sẽ mô tả ngắn gọn về chúng trong chú thích cuối trang này.

Bộ xử lý tín hiệu nâng cao (AN/UYS-1 "Proteus") là một hệ thống cỡ tủ lớn xử lý tín hiệu sóng siêu âm trong nhiều máy bay, tàu và tàu ngầm của Hải quân. Nó có tối đa bốn phần tử số học với bộ nhân và bộ cộng theo đường ống, cũng như bộ tạo sin-cosine cho FFT (biến đổi Fourier nhanh), cho phép nó thực hiện tới 60 triệu thao tác mỗi giây. Thông tin chi tiết hơn về ASP có tại đây.

Bộ xử lý mảng ASP dẫn đến sự phát triển của Bộ xử lý mảng IBM 3838 . IBM 3838 được kết nối với máy tính lớn và cung cấp các phép toán vectơ như cộng, nhân, FFT, lượng giác và đa thức. Nó có tên mã là "Gusher" vì ban đầu nó được dùng để phân tích địa chấn cho ngành dầu khí, nhưng nó cũng có thể được sử dụng để phân tích địa chấn. các ứng dụng từ mô hình thời tiết đến tính toán plasma.

Bộ xử lý tín hiệu thứ ba được đề cập trong bài viết có tên là ARP, nhưng tôi không thể tìm thấy thêm thông tin, thậm chí cả ARP là gì là viết tắt của.

(Về chủ đề máy tính System/4 Pi bí ẩn, IBM đã lên kế hoạch đưa ra một bài báo về máy tính FS-4 vào năm 1972, nhưng đã rút lại bài viết không có lời giải thích, xem Ổ cắm IBM, Rút phích cắm 'Thế hệ thứ 4'.)

Bộ xử lý tín hiệu sau này của IBM là Bộ xử lý tín hiệu chung từ năm 1986, bộ xử lý tín hiệu dựa trên VLSI là một phần của Hệ thống điện tử chiến đấu PAVE PILLAR dành cho máy bay chiến đấu chiến thuật tiên tiến. ↩

-

Theo tài liệu năm 1971, "Điều khiển và chỉ huy hệ thống/4 Pi (Model CC)", tập lệnh CC-1 "đã được thiết kế đặc biệt để tối ưu hóa hiệu quả bit lệnh cho các vấn đề thời gian thực lớn. Các tính năng bao gồm hướng dẫn đăng ký vào bộ lưu trữ định dạng ngắn (16-bit), hướng dẫn ba địa chỉ, nhiều (bốn) bộ thanh ghi chung, tự động tăng thanh ghi chỉ mục và ngắt chương trình CALL."

Nhiều tính năng trong số này tương tự như cách AP-101 tách khỏi System/360: AP-101 có hướng dẫn đăng ký để lưu trữ 16 bit, nhiều (hai) bộ thanh ghi chung, tăng địa chỉ gián tiếp tự động và lệnh gọi ngăn xếp. ↩

-

Đối với máy tính ML-1, IBM không giải thích rõ ràng tên ML. Nó được gọi là "máy tính LSI quân sự hóa của IBM", vì vậy tôi đoán rằng ML là viết tắt của "LSI quân sự hóa". ↩

-

Tên của IBM cho những con chip này trong ML-1 là "Dutchess", vì chúng được sản xuất tại nhà máy East Fishkill của IBM ở Dutchess County, New York. Thông tin thêm về chip Dutchess hiện có trên trang IBM 5100 và một bài đăng trên alt.folklore.computers . Mỗi chip được cho là chứa 134 cổng tương thích TTL: 60 cổng NAND ba đầu vào, 40 cổng NAND bốn đầu vào và 34 cổng NAND hai đầu vào. Trình điều khiển NOR. Các con chip có sự sắp xếp cố định các cổng bằng silicon có thể được nối dây khi cần thiết cho một mục đích cụ thể; IBM gọi đây là "masterslice" nhưng nó thường được gọi là mảng cổng. (Chip không phải lúc nào cũng sử dụng tất cả các cổng có sẵn, trung bình sử dụng 110 cổng.) Ưu điểm của masterslice là nó thiết kế nhanh hơn và sản xuất rẻ hơn so với chip tùy chỉnh hoàn toàn.

Vài năm sau, IBM System/38 sử dụng một masterslice lưỡng cực có chứa 704 cổng, được gắn trên một giá đỡ gốm 116 chân; nó được mô tả trong Các lớp kim loại tùy chỉnh thay đổi Chip cổng tiêu chuẩn khác nhau . Chip masterslice sau này của IBM với 1300 cổng trên mỗi chip được mô tả trong Masterslice logic lưỡng cực mật độ cao dành cho các hệ thống nhỏ. ↩

-

Owego thường bị nhầm lẫn với Oswego. Bộ phận Hệ thống Liên bang của IBM có trụ sở tại Owego, NY. Thị trấn này cách Oswego, NY 100 dặm về phía nam, nhưng tất cả mọi người từ New York Thời gian tới NASA tới EPA tới IBM chính nó trộn lẫn Owego và Oswego. Sau này là nơi đặt trụ sở của Đại học Bang New York tại Oswego. ↩

-

Nhiều bức ảnh trong bài viết này được lấy từ tập tài liệu "Hệ thống IBM/4 Pi và Hệ thống nâng cao/Máy tính 4 Pi", tháng 8 năm 1973, trong đó có thông tin chi tiết về nhiều máy tính trong họ 4 Pi. Vì tài liệu này chứa nhiều thông tin nên tôi đã quét và tải nó lên tại đây . ↩

Tác giả: zdw